74LVTH16835 Description

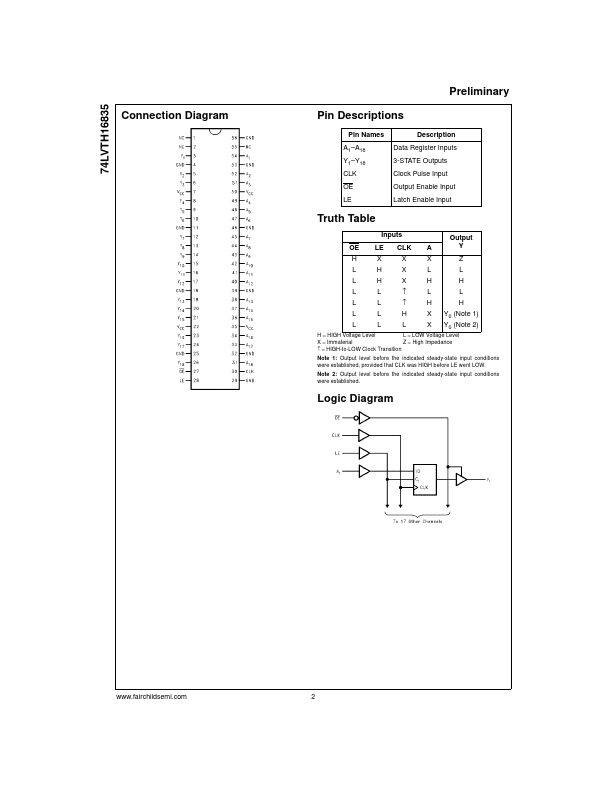

The LVTH16835 consists of 18-bit universal bus drivers which bine D-type latches and D-type flip-flops to allow data flow in transparent, latched, or clocked modes. Data flow from A to Y is controlled by the output-enable (OE) input. This device operates in the transparent mode when the latch-enable (LE) input is HIGH.