74VCX16374 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 48

Operating Voltage: 1.5 V

Description

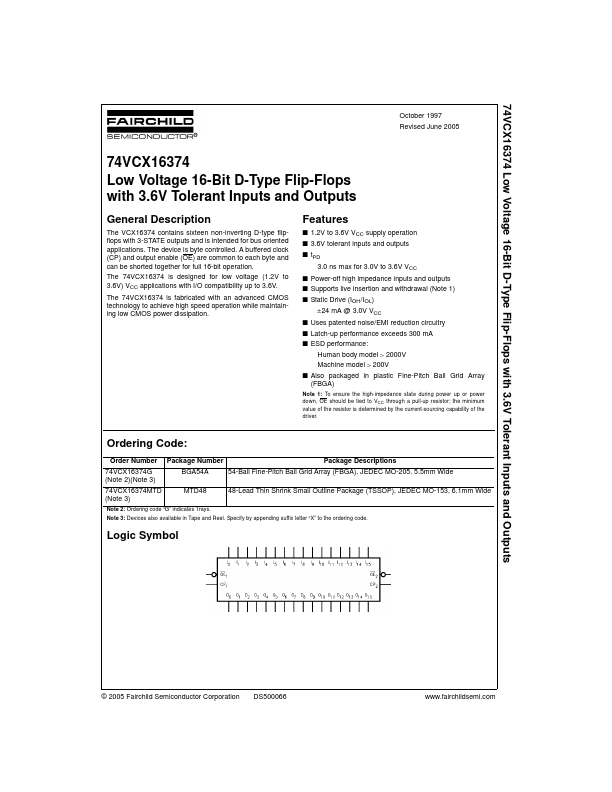

The VCX16374 contains sixteen non-inverting D-type flipflops with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled.

Key Features

- 74VCX16374MTD (Note