DM74ALS165

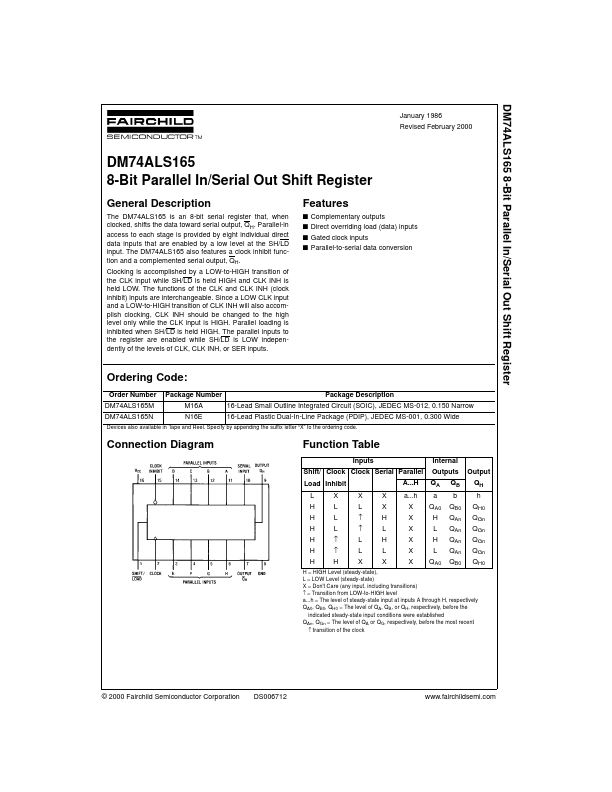

DM74ALS165 is 8-Bit Parallel In/Serial Out Shift Register manufactured by Fairchild Semiconductor.

DM74ALS165 8-Bit Parallel In/Serial Out Shift Register

January 1986 Revised February 2000

DM74ALS165 8-Bit Parallel In/Serial Out Shift Register

General Description

The DM74ALS165 is an 8-bit serial register that, when clocked, shifts the data toward serial output, QH. Parallel-in access to each stage is provided by eight individual direct data inputs that are enabled by a low level at the SH/LD input. The DM74ALS165 also Features a clock inhibit function and a plemented serial output, QH. Clocking is acplished by a LOW-to-HIGH transition of the CLK input while SH/LD is held HIGH and CLK INH is held LOW. The functions of the CLK and CLK INH (clock inhibit) inputs are interchangeable....