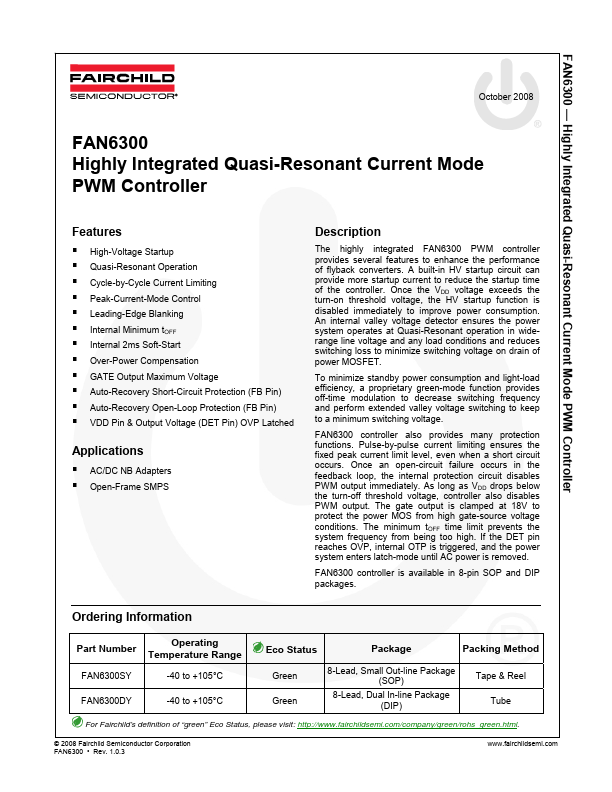

| Part | FAN6300 |

|---|---|

| Description | Highly Integrated Quasi-Resonant Current Mode PWM Controller |

| Manufacturer | Fairchild Semiconductor |

| Size | 572.05 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| FAN6300H | onsemi | Quasi-Resonant Current Mode PWM Controller |

| FAN6300A | onsemi | Quasi-Resonant Current Mode PWM Controller |