74F283

74F283 is 4-Bit Binary Full Adder manufactured by Fairchild Semiconductor.

Description

The 74F283 high-speed 4-bit binary full adder with internal carry lookahead accepts two 4-bit binary words (A0- A3, B0- B3) and a Carry input (C0). It generates the binary Sum outputs (S0- S3) and the Carry output (C4) from the most significant bit. The 74F283 will operate with either active HIGH or active LOW operands (positive or negative logic).

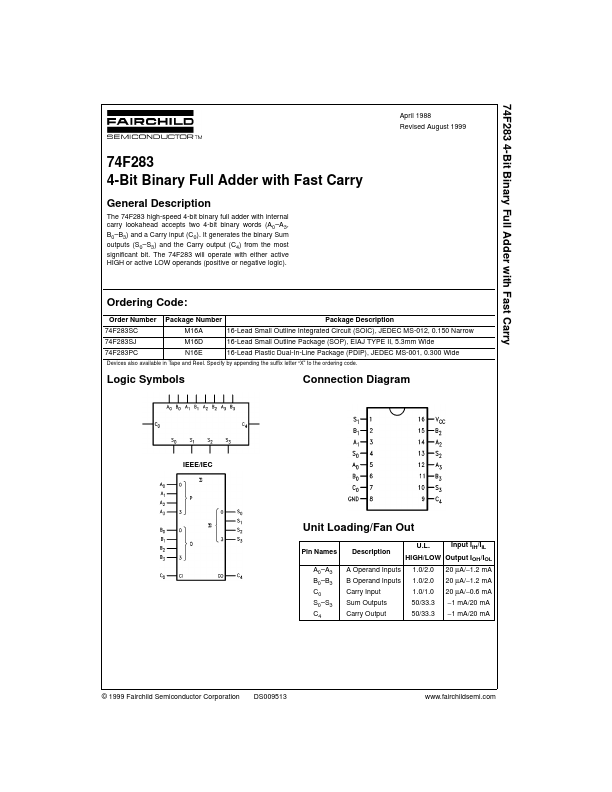

Ordering Code:

Order Number 74F283SC 74F283SJ 74F283PC Package Number M16A M16D N16E Package Description

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Logic Symbols

Connection Diagram

IEEE/IEC

Unit Loading/Fan Out

Pin Names A0- A3 B0- B3 C0 S0- S3 C4 Description

A Operand Inputs B Operand Inputs Carry Input Sum Outputs Carry Output U.L. Input IIH/IIL 20 µA/- 1.2 m A 20 µA/- 1.2 m A 20 µA/- 0.6 m A

- 1 m A/20 m A

- 1 m A/20 m A HIGH/LOW Output IOH/IOL 1.0/2.0 1.0/2.0 1.0/1.0 50/33.3 50/33.3

© 1999 Fairchild Semiconductor Corporation

DS009513

.fairchildsemi.

Functional Description

The 74F283 adds two 4-bit binary words (A plus B) plus the ining Carry (C0). The binary sum appears on the Sum (S0- S3) and outgoing carry (C4) outputs. The binary weight of the various inputs and outputs is indicated by the subscript numbers, representing powers of two. 20 (A0 + B0 + C0) + 21 (A1 + B1) + 22 (A2 + B2) + 23 (A3 + B3) = S0 + 2S1 + 4S2 + 8S3 + 16C4 Where (+) = plus Interchanging inputs of equal weight does not affect the operation. Thus C0, A0, B0 can be arbitrarily assigned to pins 5, 6 and 7 for DIPS, and 7, 8 and 9 for chip carrier packages. Due to the symmetry of the binary add function, the 74F283 can be used either with all inputs and outputs active HIGH (positive logic) or with all inputs and outputs active LOW (negative logic). See Figure 1. Note that...