24C16

Description

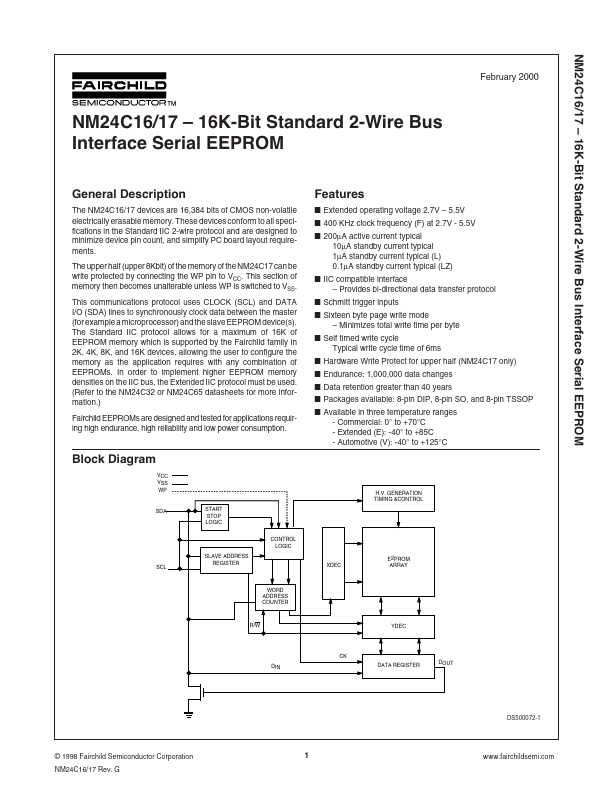

The NM24C16/17 devices are 16,384 bits of CMOS non-volatile electrically erasable memory. These devices conform to all specifications in the Standard IIC 2-wire protocol and are designed to minimize device pin count, and simplify PC board layout requirements.