24C256

24C256 is 256K-Bit 2-Wire Bus Interface Serial EEPROM manufactured by Fairchild Semiconductor.

Description

The FM24C256/C256L/C256LZ devices are 256 Kbits CMOS nonvolatile electrically erasable memory. These devices offer the designer different low voltage and low power options. They conform to all requirements in the Extended IIC 2-wire protocol. Furthermore, they are designed to minimize device pin count and simplify PC board layout requirements. The entire memory array can be write disabled (Write Protection) by connecting the WP pin to VCC. Functional address lines allow up to eight devices on the same bus, for up to a total of 2 Mbit address space. The IIC munication protocol uses CLOCK (SCL) and DATA I/O (SDA) lines to synchronously clock data between the master (for example a microprocessor) and the slave EEPROM device(s). Fairchild EEPROMs are designed and tested for applications requiring high endurance, high reliability, and low power consumption.

Features

I Extended Operating Voltages

- C256: 4.5V

- 5.5V

- C256L: 2.7V

- 5.5V

- C256LZ: 2.7V

- 5.5V I Low Power CMOS

- 1m A active current typical

- C256/C256L: 10µA standby current typical

- C256LZ: less than 1µA standby current I 2-wire IIC serial interface I 64 byte page write mode I Max write cycle time of 6ms byte/page I 40 years data retention I Endurance: 100,000 data changes I Hardware write protect for entire array I Schmitt trigger inputs for noise suppression I Electrostatic discharge protection > 4000V I 8-pin DIP and 8-pin SO (150 mil) packages. Contact factory for CSP package availability

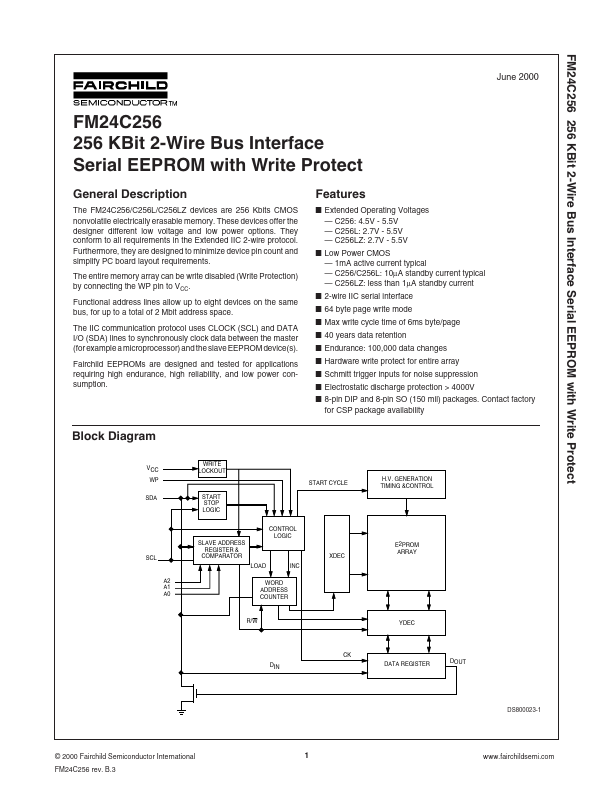

Block Diagram

VCC WP SDA START STOP LOGIC CONTROL LOGIC SLAVE ADDRESS REGISTER & PARATOR LOAD A2 A1 A0 WORD ADDRESS COUNTER INC E2PROM ARRAY WRITE LOCKOUT START CYCLE H.V. GENERATION TIMING &CONTROL

XDEC

R/W

YDEC

CK DIN DATA REGISTER DOUT

DS800023-1

© 2000 Fairchild Semiconductor International FM24C256 rev. B.3

.fairchildsemi.

FM24C256 256 KBit 2-Wire Bus Interface Serial EEPROM with Write Protect

Connection Diagram

Dual-In-Line Package (N) and 8-Pin SO Package (M8) A0 A1 A2 VSS 1 2...