Datasheet Summary

MC9S12XEP100 Reference Manual Covers MC9S12XE Family

..

HCS12 Microcontrollers

MC9S12XEP100 Rev. 1.07 05/2007 freescale.

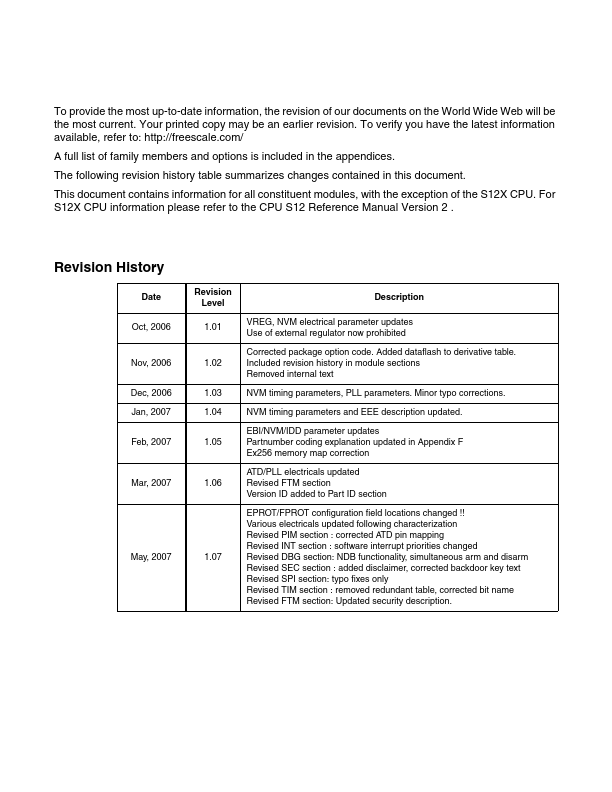

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://freescale./ A full list of family members and options is included in the appendices. The following revision history table summarizes changes contained in this document. This document contains information for all constituent modules, with the exception of the S12X CPU. For S12X CPU information please refer to...