MC9S08QE128

MC9S08QE128 is 8-Bit HCS08 Central Processor Unit manufactured by Freescale Semiconductor.

..

Freescale Semiconductor Data Sheet: Advance Information

Document Number: MC9S08QE128 Rev. 3, 06/2007

MC9S08QE128 Series

Covers: MC9S08QE128, MC9S08QE96, MC9S08QE64

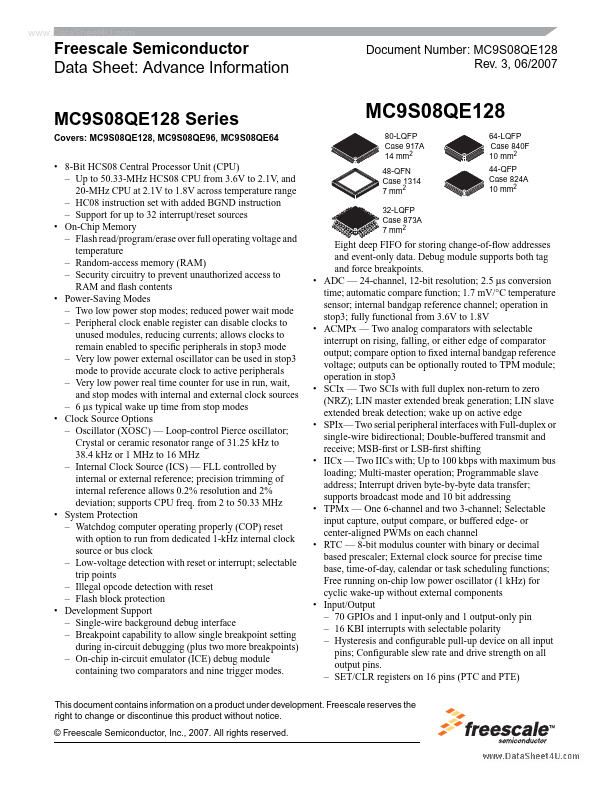

80-LQFP Case 917A 14 mm2 48-QFN Case 1314 7 mm2 32-LQFP Case 873A 7 mm2 64-LQFP Case 840F 10 mm2 44-QFP Case 824A 10 mm2

- 8-Bit HCS08 Central Processor Unit (CPU)

- Up to 50.33-MHz HCS08 CPU from 3.6V to 2.1V, and 20-MHz CPU at 2.1V to 1.8V across temperature range

- HC08 instruction set with added BGND instruction

- Support for up to 32 interrupt/reset sources

- On-Chip Memory

- Flash read/program/erase over full operating voltage and temperature

- Random-access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and flash contents

- Power-Saving Modes

- Two low power stop modes; reduced power wait mode

- Peripheral clock enable register can disable clocks to unused modules, reducing currents; allows clocks to remain enabled to specific peripherals in stop3 mode

- Very low power external oscillator can be used in stop3 mode to provide accurate clock to active peripherals

- Very low power real time counter for use in run, wait, and stop modes with internal and external clock sources

- 6 μs typical wake up time from stop modes

- Clock Source Options

- Oscillator (XOSC)

- Loop-control Pierce oscillator; Crystal or ceramic resonator range of 31.25 k Hz to 38.4 k Hz or 1 MHz to 16 MHz

- Internal Clock Source (ICS)

- FLL controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 2% deviation; supports CPU freq. from 2 to 50.33 MHz

- System Protection

- Watchdog puter operating properly (COP) reset with option to run from dedicated 1-k Hz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode detection with reset

- Flash block protection

- Development Support

- Single-wire background debug interface

- Breakpoint capability to allow single breakpoint...