GS71116TU Overview

Description

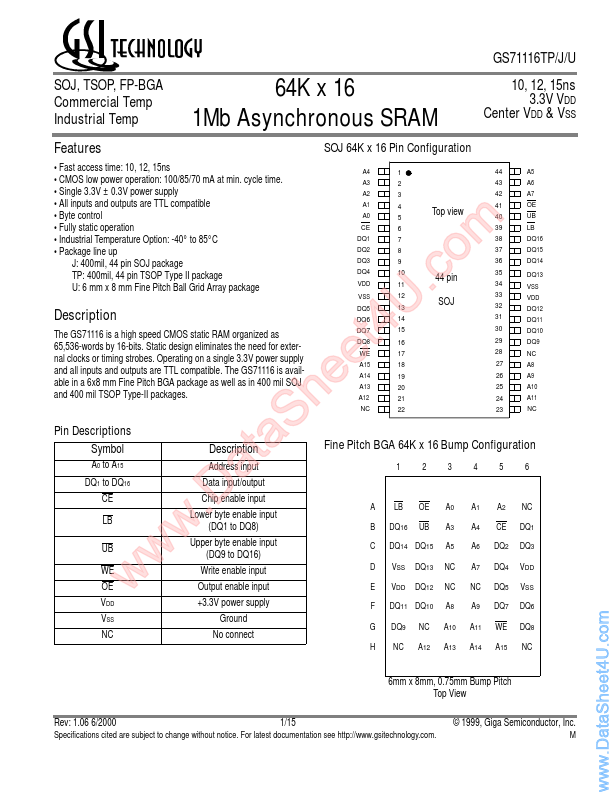

The GS71116 is a high speed CMOS static RAM organized as 65,536-words by 16-bits. Static design eliminates the need for external clocks or timing strobes.

Key Features

- Fast access time: 10, 12, 15ns

- CMOS low power operation: 100/85/70 mA at min. cycle time

- Single 3.3V ± 0.3V power supply

- All inputs and outputs are TTL compatible

- Fully static operation

- Industrial Temperature Option: -40° to 85°C