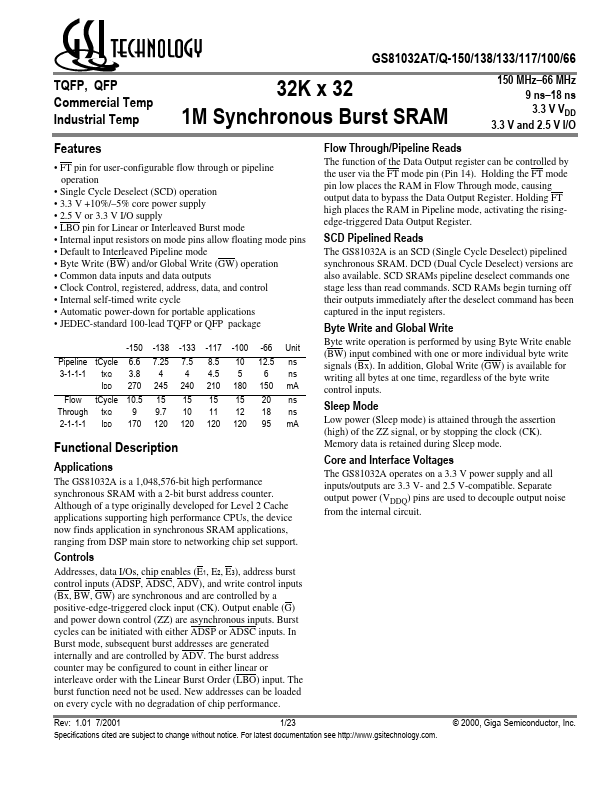

GS81032AT

Features

- FT pin for user-configurable flow through or pipeline operation

- Single Cycle Deselect (SCD) operation

- 3.3 V +10%/- 5% core power supply

- 2.5 V or 3.3 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to Interleaved Pipeline mode

- Byte Write (BW) and/or Global Write (GW) operation

- mon data inputs and data outputs

- Clock Control, registered, address, data, and control

- Internal self-timed write cycle

- Automatic power-down for portable applications

- JEDEC-standard 100-lead TQFP or QFP package -150 Pipeline t Cycle 6.6 3-1-1-1 t KQ 3.8 IDD 270 Flow t Cycle 10.5 Through t KQ 9 2-1-1-1 IDD 170 -138 -133 7.25 7.5 4 4 245 240 15 15 9.7 10 120 120 -117 8.5 4.5 210 15 11 120 -100 10 5 180 15 12 120 -66 12.5 6 150 20 18 95 Unit ns ns m A ns ns m A

32K x 32 1M Synchronous Burst SRAM

Flow Through/Pipeline Reads

150 MHz- 66 MHz 9 ns- 18 ns 3.3 V VDD 3.3 V and 2.5 V I/O

The function of the Data...