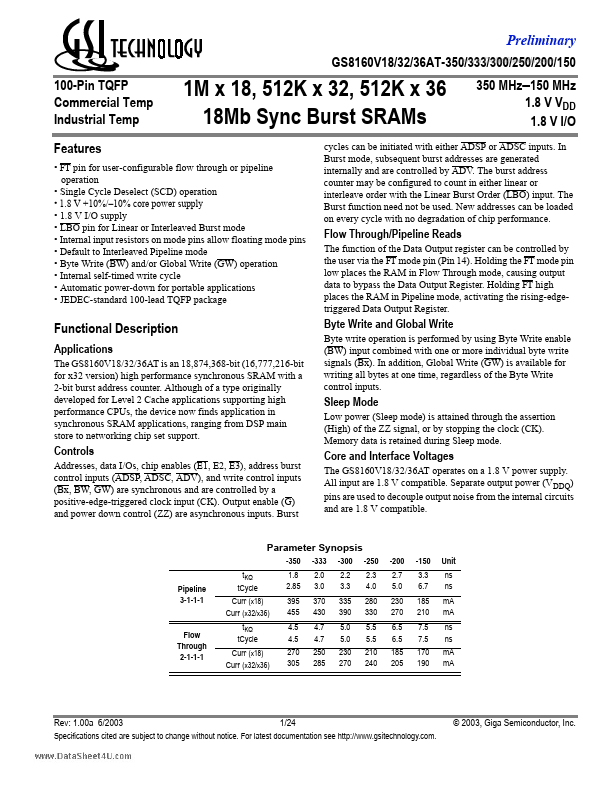

GS8160V36AT Description

Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support. Byte Write and Global Write Byte write operation is performed by using Byte Write enable (BW) input bined with one or more individual byte write signals (Bx). In addition, Global Write...

GS8160V36AT Key Features

- FT pin for user-configurable flow through or pipeline operation

- Single Cycle Deselect (SCD) operation

- 1.8 V +10%/-10% core power supply

- 1.8 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to Interleaved Pipeline mode

- Byte Write (BW) and/or Global Write (GW) operation

- Internal self-timed write cycle

- Automatic power-down for portable