Datasheet Summary

GS8170LW36/72C-333/300/250/200

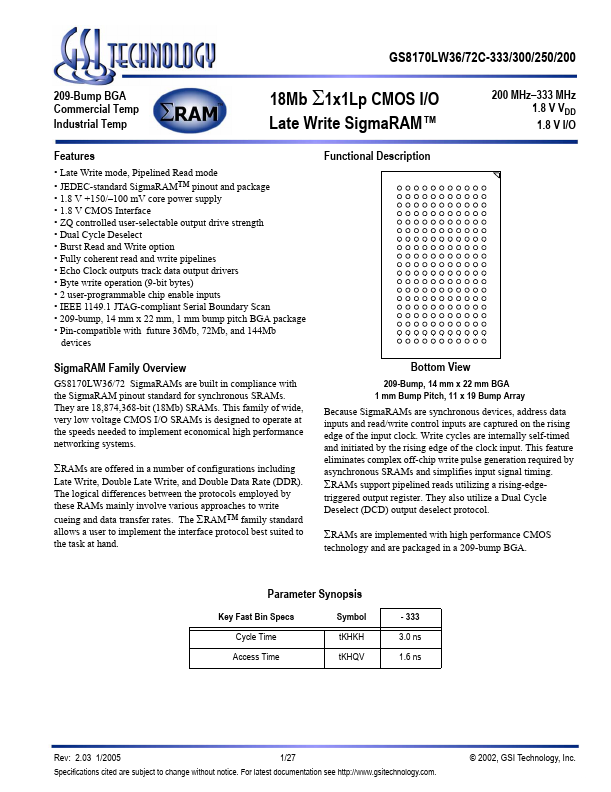

209-Bump BGA mercial Temp Industrial Temp Features

- Late Write mode, Pipelined Read mode

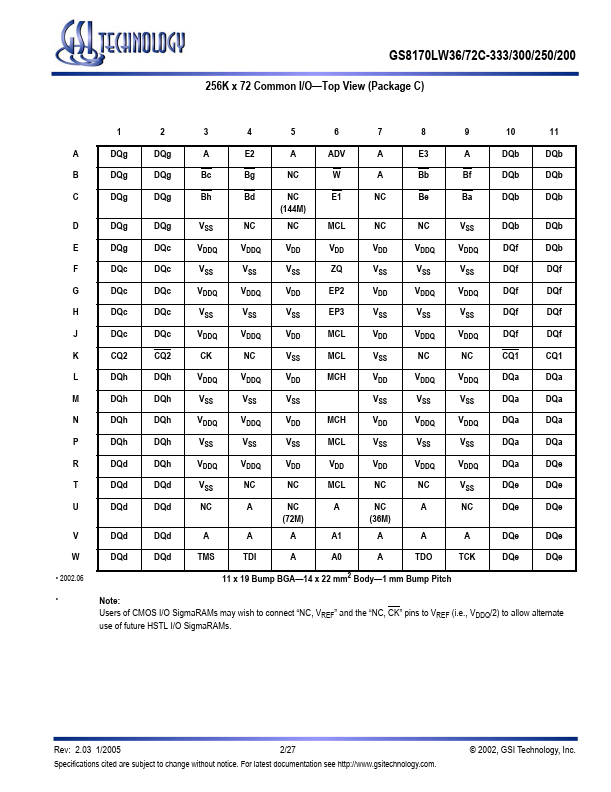

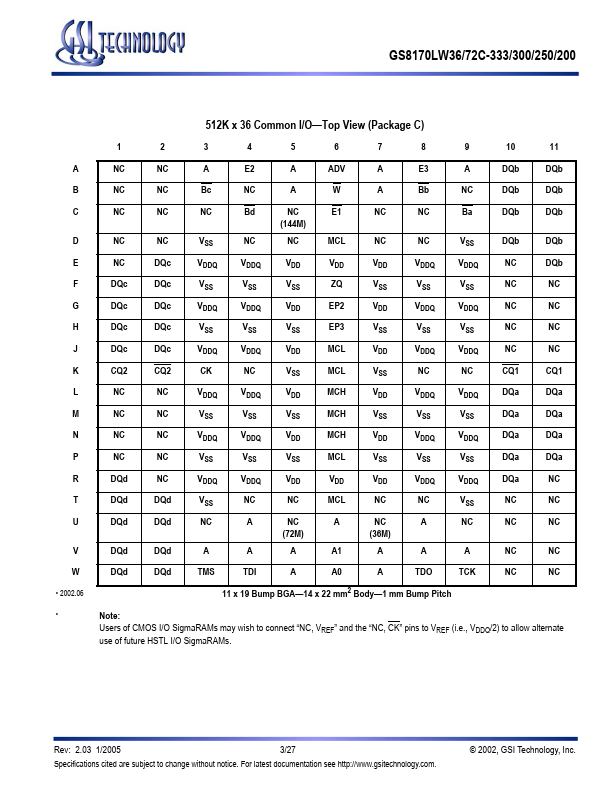

- JEDEC-standard SigmaRAM™ pinout and package

- 1.8 V +150/- 100 mV core power supply

- 1.8 V CMOS Interface

- ZQ controlled user-selectable output drive strength

- Dual Cycle Deselect

- Burst Read and Write option

- Fully coherent read and write pipelines

- Echo Clock outputs track data output drivers

- Byte write operation (9-bit bytes)

- 2 user-programmable chip enable inputs

- IEEE 1149.1 JTAG-pliant Serial Boundary Scan

- 209-bump, 14 mm x 22 mm, 1 mm bump pitch BGA package

- Pin-patible with future 36Mb, 72Mb, and 144Mb devices

18Mb Σ1x1Lp CMOS I/O Late...