Datasheet Summary

..

Preliminary GS864018/32/36T-xxxV

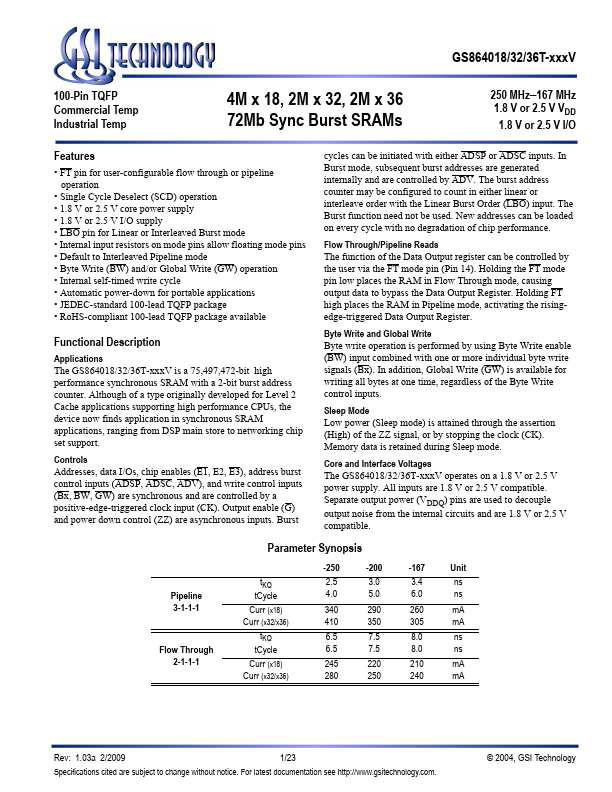

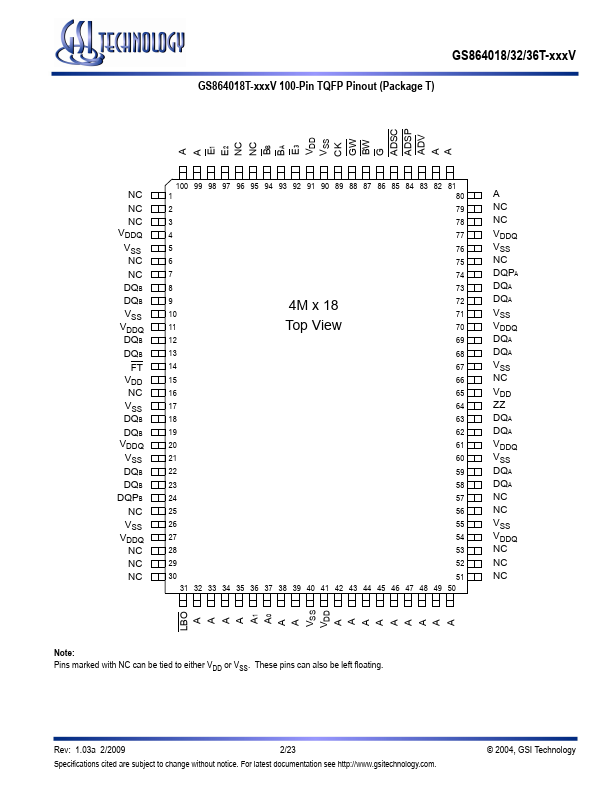

100-Pin TQFP mercial Temp Industrial Temp Features

4M x 18, 2M x 32, 2M x 36 72Mb Sync Burst SRAMs

250 MHz- 167 MHz 1.8 V or 2.5 V VDD 1.8 V or 2.5 V I/O

- FT pin for user-configurable flow through or pipeline operation

- Single Cycle Deselect (SCD) operation

- 1.8 V or 2.5 V core power supply

- 1.8 V or 2.5 V I/O supply

- LBO pin for Linear or Interleaved Burst mode

- Internal input resistors on mode pins allow floating mode pins

- Default to Interleaved Pipeline mode

- Byte Write (BW) and/or Global Write (GW) operation

- Internal self-timed write cycle

- Automatic power-down for portable applications

- JEDEC-standard 100-lead...