GS8662S18E-333

GS8662S18E-333 is DDR SigmaSIO-II SRAM manufactured by GSI Technology.

- Part of the GS8662S08E-333 comparator family.

- Part of the GS8662S08E-333 comparator family.

Preliminary GS8662S08/09/18/36E-333/300/250/200/167 ..

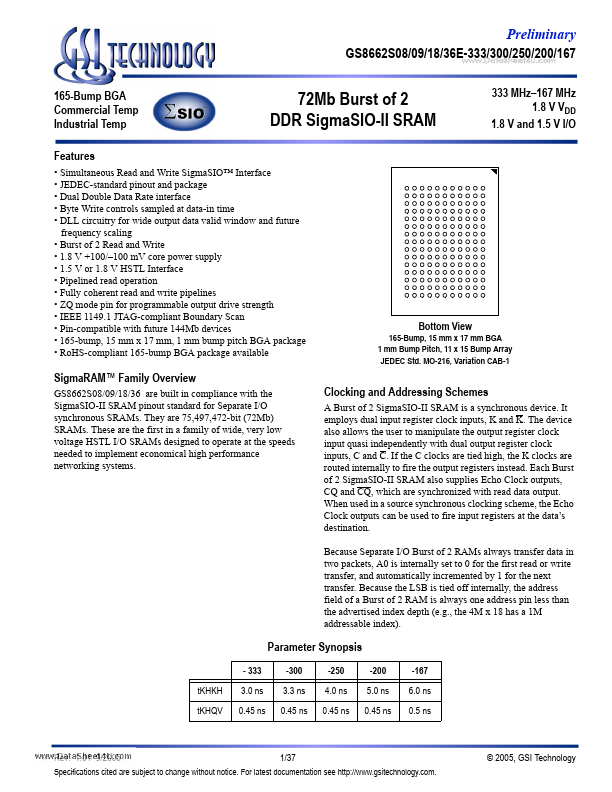

165-Bump BGA mercial Temp Industrial Temp Features

- Simultaneous Read and Write SigmaSIO™ Interface

- JEDEC-standard pinout and package

- Dual Double Data Rate interface

- Byte Write controls sampled at data-in time

- DLL circuitry for wide output data valid window and future frequency scaling

- Burst of 2 Read and Write

- 1.8 V +100/- 100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation

- Fully coherent read and write pipelines

- ZQ mode pin for programmable output drive strength

- IEEE 1149.1 JTAG-pliant Boundary Scan

- Pin-patible with future 144Mb devices

- 165-bump, 15 mm x...