GS8692DT19LE

Features

- Aerospace-Level Product

- 2.0 clock Latency with DLL on

- 1.0 clock Latency with DLL off

- Optional DLL-controlled output timing

- Can be operated with DLL on or off

- Simultaneous Read and Write Sigma Quad™ Interface

- JEDEC-standard pinout and package

- Dual Double Data Rate interface

- Byte Write controls sampled at data-in time

- Burst of 4 Read and Write

- Dual-Range On-Die Termination (ODT) on Data (D), Byte

Write (BW), and Clock (K, K) inputs

- 1.8 V +100/- 100 m V core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation

- Fully coherent read and write pipelines

- ZQ pin for programmable output drive strength

- Data Valid Pin (QVLD) Support

- IEEE 1149.1 JTAG-pliant Boundary Scan

- 165-bump Ceramic Column Grid Array (CCGA) and

165-bump Land Grid Array (LGA) packages

Radiation Performance

- Total Ionizing Dose (TID) > 100krads(Si)

- Single Event Latchup Immunity > 77.3 Me V.cm2/mg (125C)

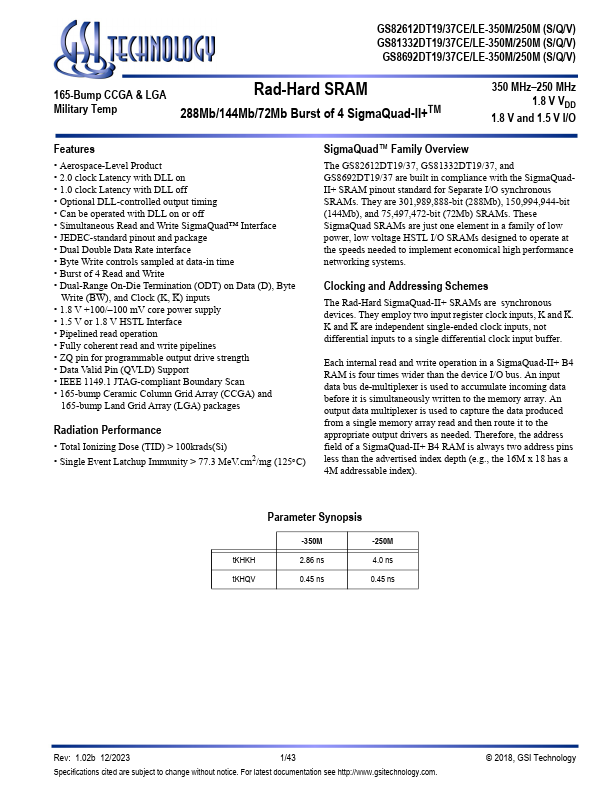

Sigma Quad™ Family Overview

The GS82612DT19/37, GS81332DT19/37,...