Datasheet Summary

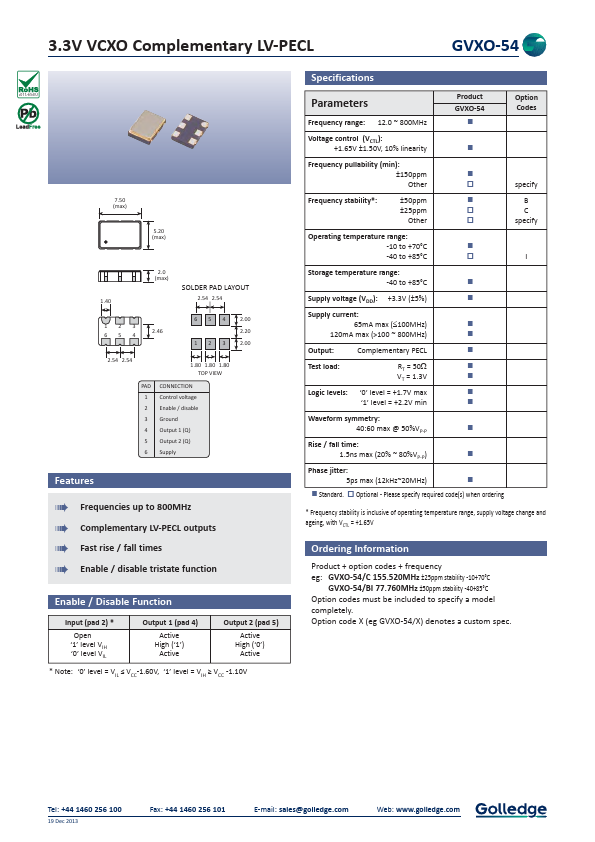

3.3V VCXO plementary LV-PECL

2011/65/EU

7.50 (max)

5.20 (max)

2.0 (max)

SOLDER PAD LAYOUT

1.40 2.54 2.54

123 654

654 123

2.00 2.20 2.00

2.54 2.54

1.80 1.80 1.80 TOP VIEW

PAD CONNECTION 1 Control voltage 2 Enable / disable 3 Ground 4 Output 1 (Q) 5 Output 2 (Q) 6 Supply

Features

Frequencies up to 800MHz plementary LV-PECL outputs Fast rise / fall times Enable / disable tristate function

Enable / Disable Function

Input (pad 2)

- Open ‘1’ level VIH ‘0’ level VIL

Output 1 (pad 4)

Active High (‘1’)

Active

Output 2 (pad 5)

Active High (‘0’)

Active

- Note: ‘0’ level = VIL ≤ VCC-1.60V, ‘1’ level = VIH ≥ VCC -1.10V

Specifications

Parameters

Frequency...