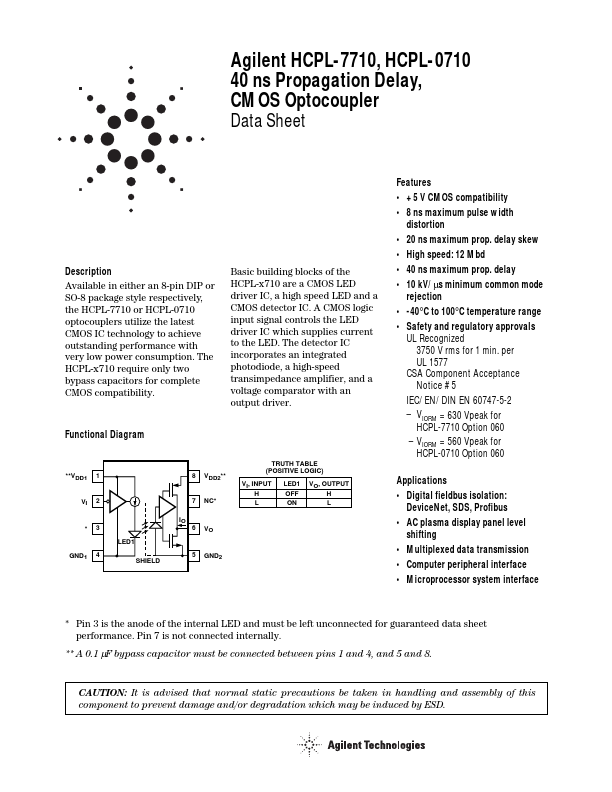

HCPL-7710

Key Features

- +5 V CMOS compatibility

- 8 ns maximum pulse width distortion

- 20 ns maximum prop. delay skew

- High speed: 12 Mbd

- 40 ns maximum prop. delay

- 10 kV/µs minimum common mode rejection

- -40°C to 100°C temperature range

- Safety and regulatory approvals UL Recognized 3750 V rms for 1 min. per UL 1577 CSA Component Acceptance Notice #5 IEC/EN/DIN EN 60747-5-2 - VIORM = 630 Vpeak for HCPL-7710 Option 060 - VIORM = 560 Vpeak for HCPL-0710 Option 060 Applications

- Digital fieldbus isolation: DeviceNet, SDS, Profibus

- AC plasma display panel level shifting