74173

Overview

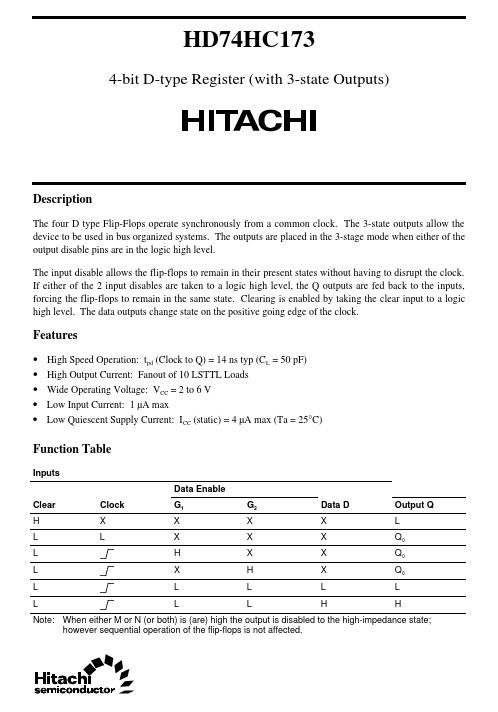

The four D type Flip-Flops operate synchronously from a common clock. The 3-state outputs allow the device to be used in bus organized systems.

- High Speed Operation: tpd (Clock to Q) = 14 ns typ (CL = 50 pF) High Output Current: Fanout of 10 LSTTL Loads Wide Operating Voltage: VCC = 2 to 6 V Low Input Current: 1 µA max Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)