HD74HC386 Description

Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse if the enable input G is low. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D input signal has no effect at the output.

HD74HC386 Key Features

- High Speed Operation: tpd = 13 ns typ (CL = 50 pF) High Output Current: Fanout of 10 LSTTL Loads Wide Operating Voltage:

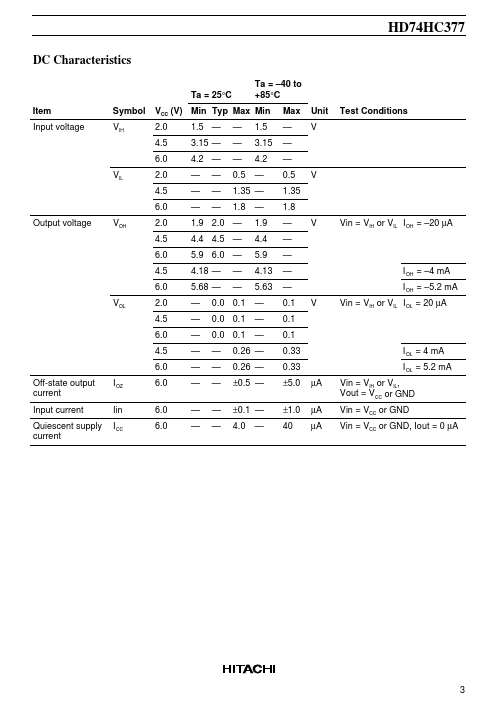

- 0.5 1.35 1.8

- 0.5 1.5 3.15 4.2

- 1.9 4.4 5.9 4.13 5.63

- Output voltage

- 4.4 4.5

- 5.9 6.0

- Off-state output current Input current Quiescent supply current

- 95 19 16 10 pF ns ns ns ns ns Unit MHz Test Conditions

- 6 30 35