HD74HC390

Description

The HD74HC390 incorporate dual decade counters, each posed of a divide-by-two and a divide-byfive counter. The divide-by-two and divide-by-five counters can be cascaded to form dual decade, dual biquinary, or various binations up to a single divide-by-100 counter. The HD74HC390 is incremented on the high to low transition (negative edge) of the clock input, and each has an independent clear input. When clear is set high all four bits of each counter are set to a low level. This enables count truncation and allows the implementation of divide-by-N counter configurations.

Features

- -

- -

- High Speed Operation: tpd (Clock A to QA) = 11 ns typ (CL = 50 p F) High Output Current: Fanout of 10 LSTTL Loads Wide Operating Voltage: VCC = 2 to 6 V Low Input Current: 1 µA max Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)

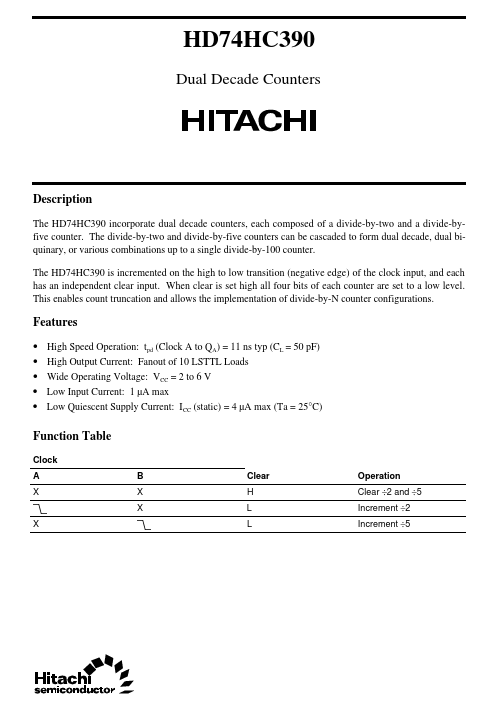

Function Table

Clock A X B X X X Clear H L L Operation Clear ÷2 and ÷5 Increment ÷2 Increment ÷5

Pin Arrangement

1A 1Clear 1QA...