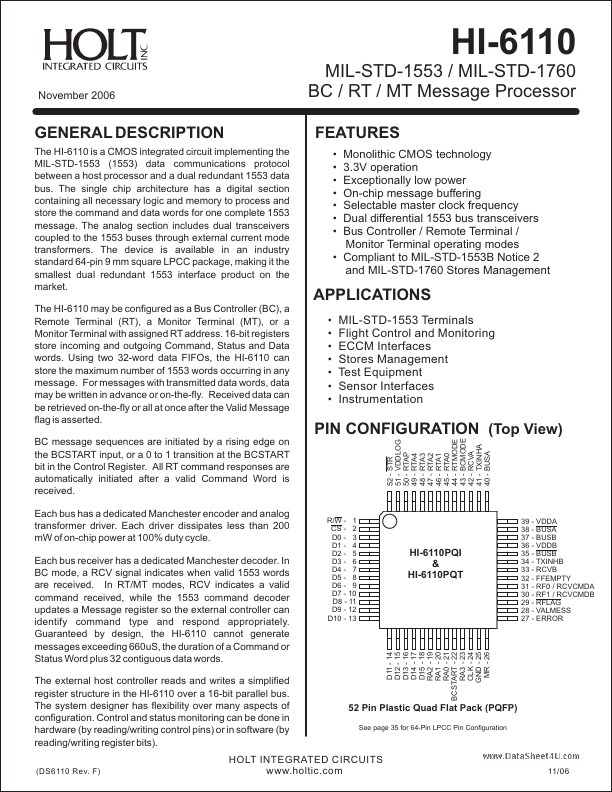

HI-6110

Description

The HI-6110 is a CMOS integrated circuit implementing the MIL-STD-1553 (1553) data communications protocol between a host processor and a dual redundant 1553 data bus. The single chip architecture has a digital section containing all necessary logic and memory to process and store the command and data words for one complete 1553 message.

Key Features

- Monolithic CMOS technology 3.3V operation Exceptionally low power On-chip message buffering Selectable master clock frequency Dual differential 1553 bus transceivers Bus Controller / Remote Terminal / Monitor Terminal operating modes

- Compliant to MIL-STD-1553B Notice 2 and MIL-STD-1760 Stores Management