HI-8482

Description

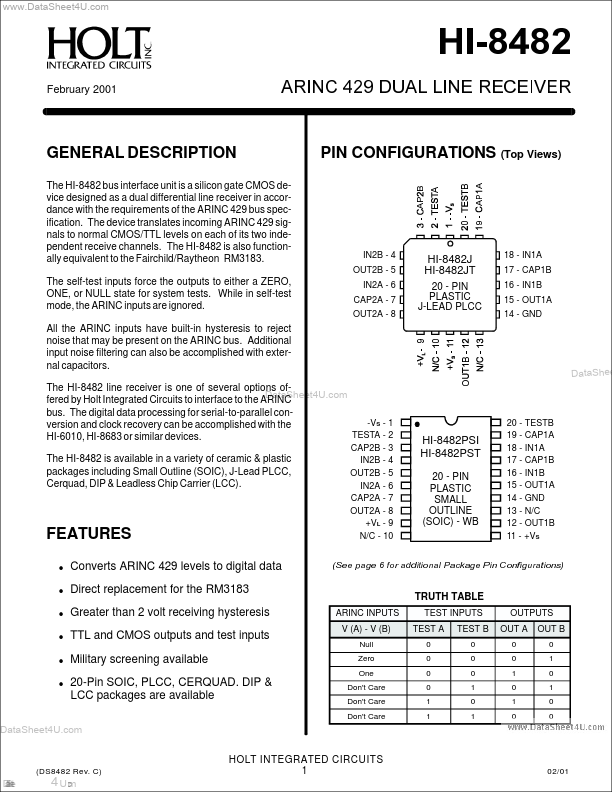

The HI-8482 bus interface unit is a silicon gate CMOS device designed as a dual differential line receiver in accordance with the requirements of the ARINC 429 bus specification. The device translates incoming ARINC 429 signals to normal CMOS/TTL levels on each of its two independent receive channels.