HMS9XC7132 Key Features

- 37 13.3 Low VDD voltage reset

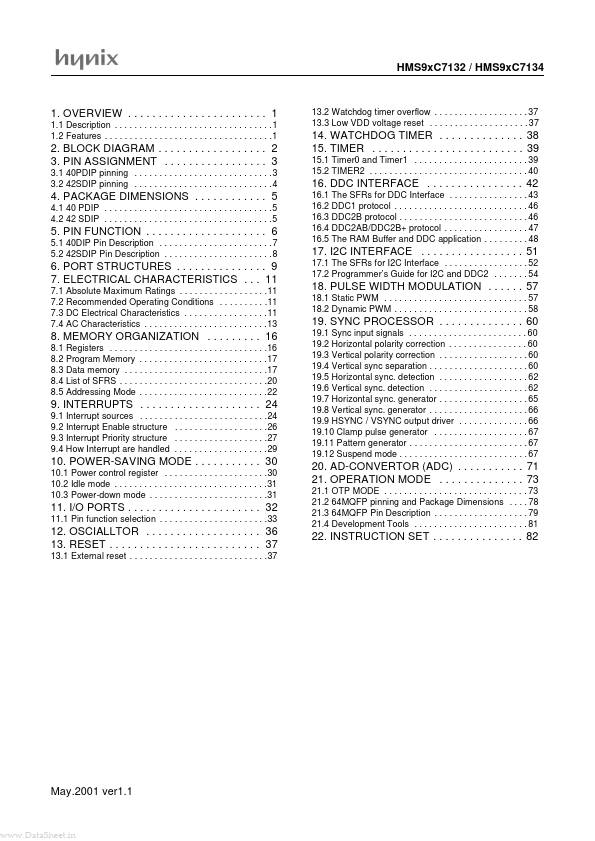

- 2 3. PIN ASSIGNMENT

- 3 3.2 42SDIP pinning

- 38 15. TIMER

- 39 15.2 TIMER2

- 43 16.2 DDC1 protocol

- 46 16.3 DDC2B protocol

- 46 16.4 DDC2AB/DDC2B+ protocol

- 47 16.5 The RAM Buffer and DDC application

- 5 4.2 42 SDIP