HY27UG084G2D

features

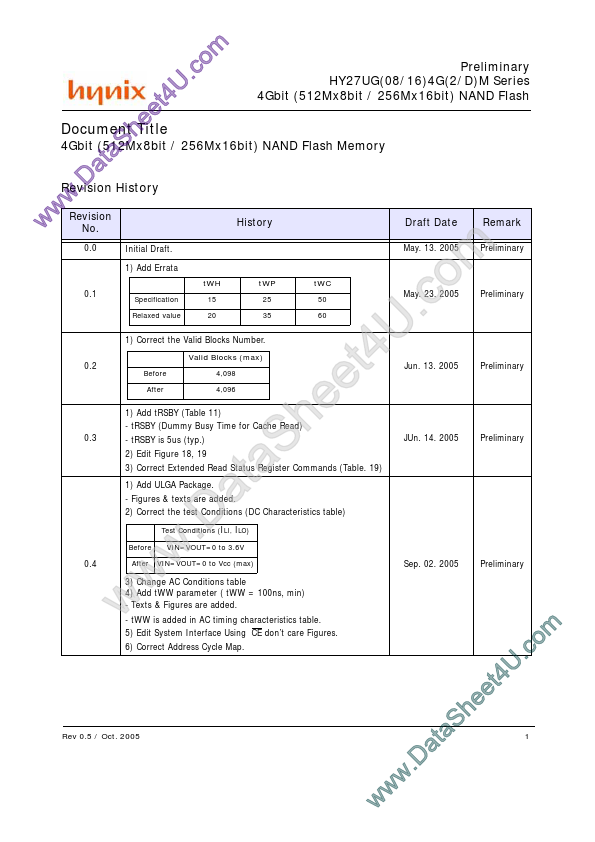

. 9) Change DC Characteristics (Table 8)

- Operating Current ICC1 Typ Before 0.4 After 20 25 Max 40 45 ICC2 Typ 20 25 Max 40 45 ICC3 Typ 20 25 Max 40 45 Sep. 16. 2005 Preliminary

10) Change AC Characteristics

- Errata is deleted. t WC Before After 60ns 50ns t WP 35ns 25ns t WH 20ns 15ns

- t R is changed. t R Before After 0.5 25us 30us Oct. 05. 2005 Preliminary

1) Delete Concurrent Operation.

Rev 0.5 / Oct. 2005

Preliminary HY27UG(08/16)4G(2/D)M Series 4Gbit (512Mx8bit / 256Mx16bit) NAND Flash FEATURES

SUMMARY

HIGH DENSITY NAND FLASH MEMORIES

- Cost effective solutions for mass storage applications NAND INTERFACE

- x8 bus width.

- Multiplexed Address/ Data

- Pinout patibility for all densities FAST BLOCK ERASE

- Block erase time: 2ms (Typ.)

STATUS REGISTER ELECTRONIC SIGNATURE

- Manufacturer Code

- Device Code CHIP ENABLE DON'T CARE OPTION

- Simple interface with microcontroller AUTOMATIC PAGE 0 READ AT POWER-UP OPTION

- Boot from NAND support

- Automatic Memory Download...