HYMD216726A6

HYMD216726A6 is Unbuffered DDR SO-DIMM manufactured by SK Hynix.

.Data Sheet.co.kr

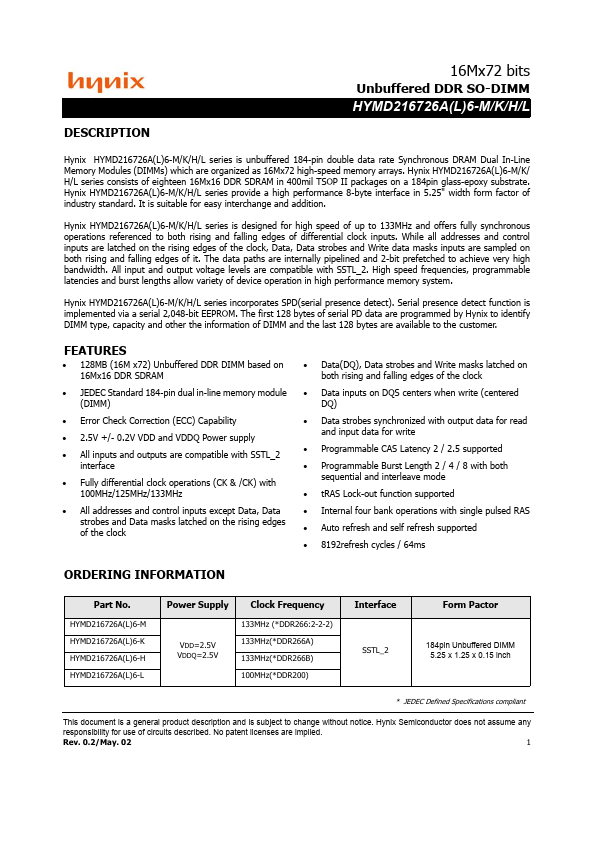

16Mx72 bits

Unbuffered DDR SO-DIMM

HYMD216726A(L)6-M/K/H/L

DESCRIPTION

Hynix HYMD216726A(L)6-M/K/H/L series is unbuffered 184-pin double data rate Synchronous DRAM Dual In-Line Memory Modules (DIMMs) which are organized as 16Mx72 high-speed memory arrays. Hynix HYMD216726A(L)6-M/K/ H/L series consists of eighteen 16Mx16 DDR SDRAM in 400mil TSOP II packages on a 184pin glass-epoxy substrate. Hynix HYMD216726A(L)6-M/K/H/L series provide a high performance 8-byte interface in 5.25" width form factor of industry standard. It is suitable for easy interchange and addition. Hynix HYMD216726A(L)6-M/K/H/L series is designed for high speed of up to 133MHz and offers fully synchronous operations referenced to both rising and falling edges of differential clock inputs. While all addresses and control inputs are latched on the rising edges of the clock, Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 2-bit prefetched to achieve very high bandwidth. All input and output voltage levels are patible with SSTL_2. High speed frequencies, programmable latencies and burst lengths allow variety of device operation in high performance memory system. Hynix HYMD216726A(L)6-M/K/H/L series incorporates SPD(serial presence detect). Serial presence detect function is implemented via a serial 2,048-bit EEPROM. The first 128 bytes of serial PD data are programmed by Hynix to identify DIMM type, capacity and other the information of DIMM and the last 128 bytes are available to the customer.

Features

- -

- -

- -

- 128MB (16M x72) Unbuffered DDR DIMM based on 16Mx16 DDR SDRAM JEDEC Standard 184-pin dual in-line memory module (DIMM) Error Check Correction (ECC) Capability 2.5V +/- 0.2V VDD and VDDQ Power supply All inputs and outputs are patible with SSTL_2 interface Fully differential clock operations (CK & /CK) with 100MHz/125MHz/133MHz All addresses and control inputs...