HYMD232G726DF8N-D43J

Overview

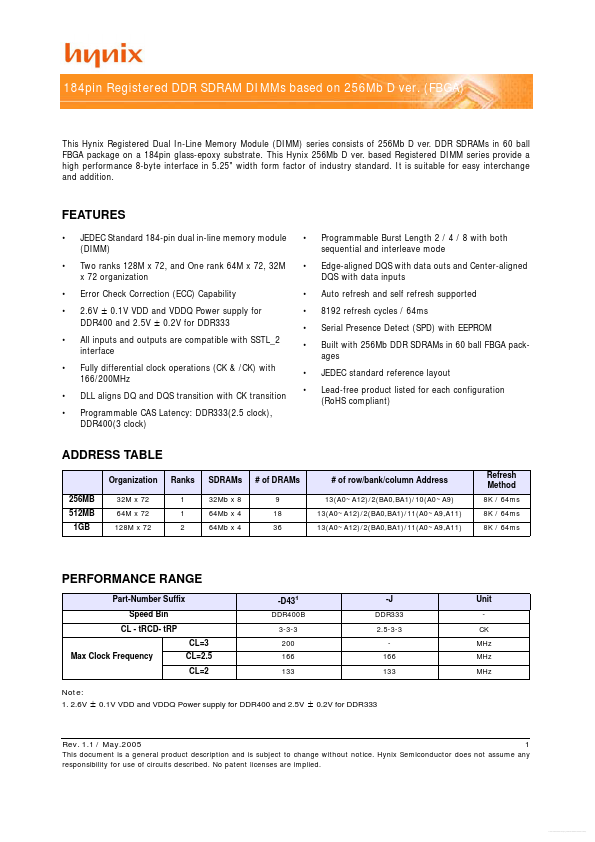

- JEDEC Standard 184-pin dual in-line memory module (DIMM) Two ranks 128M x 72, and One rank 64M x 72, 32M x 72 organization Error Check Correction (ECC) Capability 2.6V ± 0.1V VDD and VDDQ Power supply for DDR400 and 2.5V ± 0.2V for DDR333 All inputs and outputs are compatible with SSTL_2 interface Fully differential clock operations (CK & /CK) with 166/200MHz DLL aligns DQ and DQS transition with CK transition Programmable CAS Latency: DDR333(2.5 clock), DDR400(3 clock) * * * * * * *

- Programmable Burst Length 2 / 4 / 8 with both sequential and interleave mode Edge-aligned DQS with data outs and Center-aligned DQS with data inputs Auto refresh and self refresh supported 8192 refresh cycles / 64ms Serial Presence Detect (SPD) with EEPROM Built with 256Mb DDR SDRAMs in 60 ball FBGA packages JEDEC standard reference layout Lead-free product listed for each configuration (RoHS compliant)