ICS432I-101 Key Features

- Dual differential 3.3V LVPECL outputs

- Selectable CLK, nCLK or LVCMOS/LVTTL TEST_CLK

- TEST_CLK can accept the following input levels: LVCMOS or LVTTL

- CLK, nCLK pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- CLK, nCLK or TEST_CLK maximum input frequency: 40MHz

- Output frequency range: 25MHz to 700MHz

- VCO range: 250MHz to 700MHz

- Accepts any single-ended input signal on CLK input with resistor bias on nCLK input

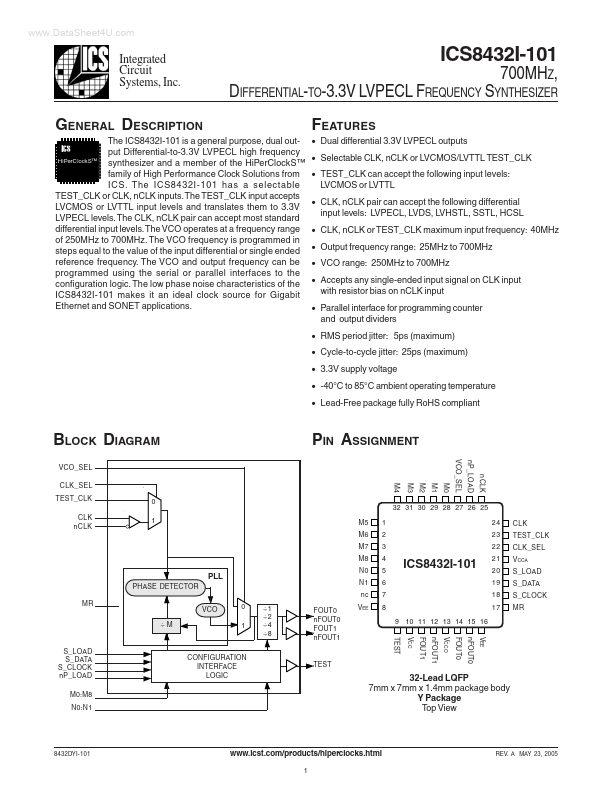

- Parallel interface for programming counter and output dividers

- RMS period jitter: 5ps (maximum)