ICS557-08 Overview

Description

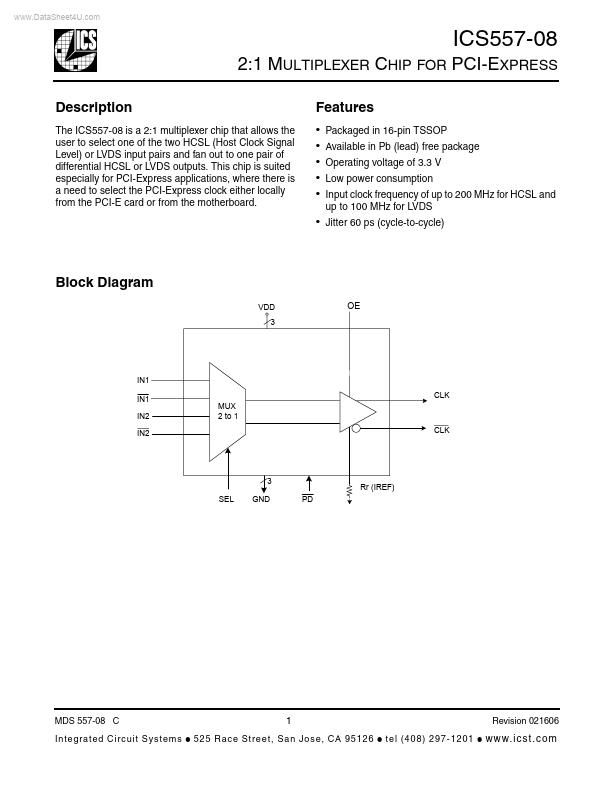

The ICS557-08 is a 2:1 multiplexer chip that allows the user to select one of the two HCSL (Host Clock Signal Level) or LVDS input pairs and fan out to one pair of differential HCSL or LVDS outputs. This chip is suited especially for PCI-Express applications, where there is a need to select the PCI-Express clock either locally from the PCI-E card or from the motherboard.

Key Features

- Jitter 60 ps (cycle-to-cycle)