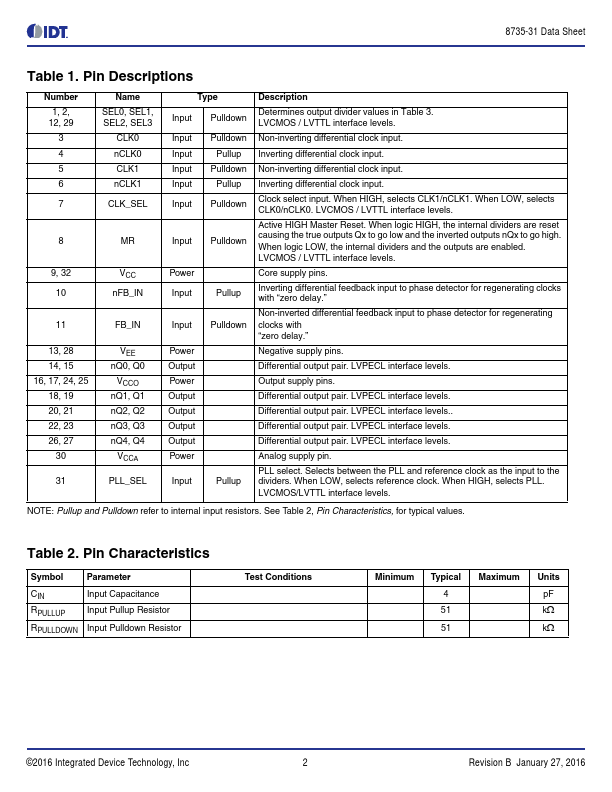

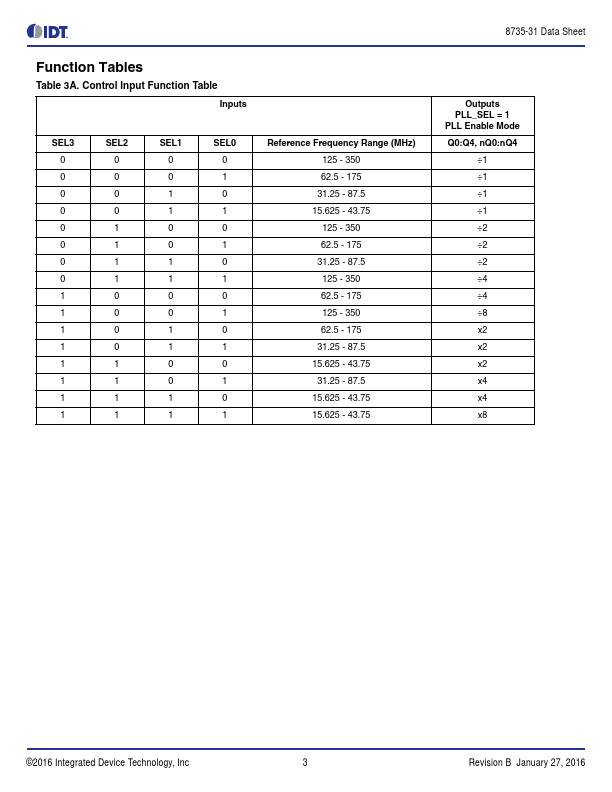

Datasheet Summary

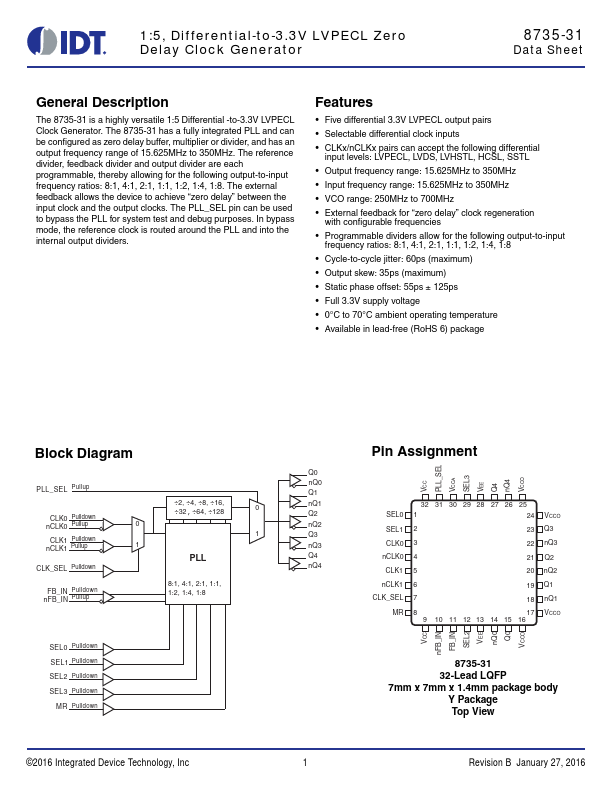

1:5, Differential-to-3.3V LVPECL Zero Delay Clock Generator

Data Sheet

General Description

The 8735-31 is a highly versatile 1:5 Differential -to-3.3V LVPECL Clock Generator. The 8735-31 has a fully integrated PLL and can be configured as zero delay buffer, multiplier or divider, and has an output frequency range of 15.625MHz to 350MHz. The reference divider, feedback divider and output divider are each programmable, thereby allowing for the following output-to-input frequency ratios: 8:1, 4:1, 2:1, 1:1, 1:2, 1:4, 1:8. The external feedback allows the device to achieve “zero delay” between the input clock and the output clocks. The PLL_SEL pin can be used to bypass the PLL for...