89HPES8T5A

89HPES8T5A is 8-Lane 5-Port PCI Express Switch manufactured by IDT.

Overview

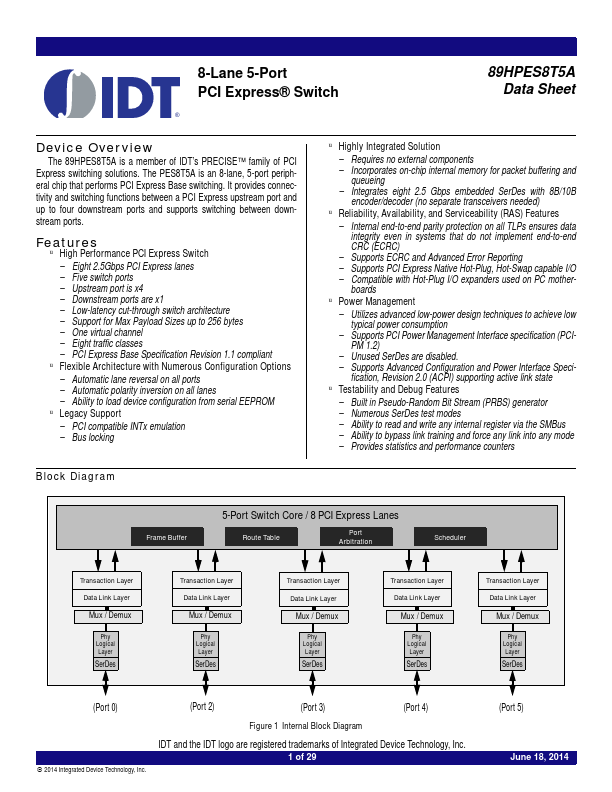

- The 89HPES8T5A is a member of IDT’s PRECISE™ family of PCI Express switching solutions. The PES8T5A is an 8-lane, 5-port peripheral chip that performs PCI Express Base switching. It provides connectivity and switching functions between a PCI Express upstream port and up to four downstream ports and supports switching between downstream ports.

- -

Features

- -

High Performance PCI Express Switch

- Eight 2.5Gbps PCI Express lanes

- Five switch ports

- Upstream port is x4

- Downstream ports are x1

- Low-latency cut-through switch architecture

- Support for Max Payload Sizes up to 256 bytes

- One virtual channel

- Eight traffic classes

- PCI Express Base Specification Revision 1.1 pliant Flexible Architecture with Numerous Configuration Options

- Automatic lane reversal on all ports

- Automatic polarity inversion on all lanes

- Ability to load device configuration from serial EEPROM Legacy Support

- PCI patible INTx emulation

- Bus locking

- -

Highly Integrated Solution

- Requires no external ponents

- Incorporates on-chip internal memory for packet buffering and queueing

- Integrates eight 2.5 Gbps embedded Ser Des with 8B/10B encoder/decoder (no separate transceivers needed) Reliability, Availability, and Serviceability (RAS) Features

- Internal end-to-end parity protection on all TLPs ensures data integrity even in systems that do not implement end-to-end CRC (ECRC)

- Supports ECRC and Advanced Error Reporting

- Supports PCI Express Native Hot-Plug, Hot-Swap capable I/O

- patible with Hot-Plug I/O expanders used on PC motherboards Power Management

- Utilizes advanced low-power design techniques to achieve low typical power consumption

- Supports PCI Power Management Interface specification (PCIPM 1.2)

- Unused Ser Des are disabled.

- Supports Advanced Configuration and Power Interface Specification, Revision 2.0 (ACPI) supporting active link state Testability and Debug Features

- Built in Pseudo-Random Bit Stream (PRBS) generator

- Numerous Ser Des...