9DBL07P1 Overview

Description

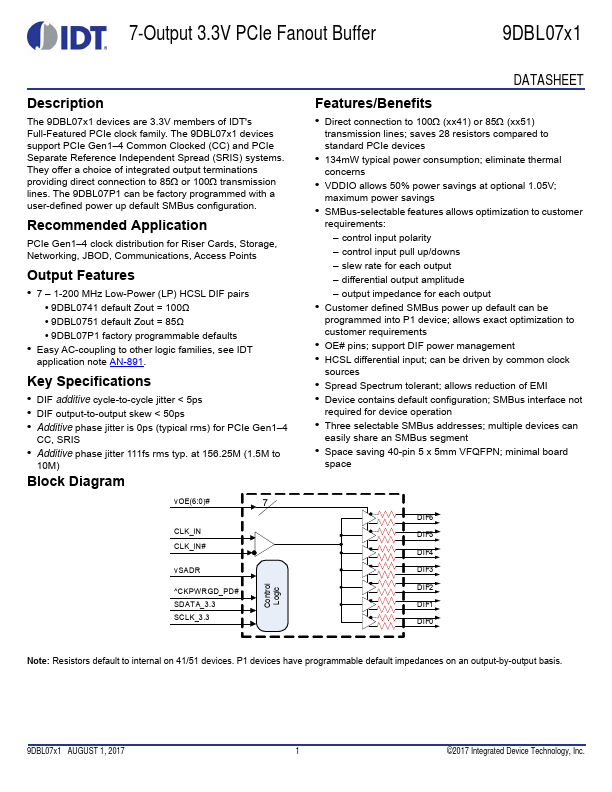

The 9DBL07x1 devices are 3.3V members of IDT's Full-Featured PCIe clock family. The 9DBL07x1 devices support PCIe Gen1–4 Common Clocked (CC) and PCIe Separate Reference Independent Spread (SRIS) systems.

Key Features

- 7 – 1-200 MHz Low-Power (LP) HCSL DIF pairs

- 9DBL0741 default Zout = 100Ω

- 9DBL0751 default Zout = 85Ω

- 9DBL07P1 factory programmable defaults

- Easy AC-coupling to other logic families, see IDT