9FGU0431 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 32

Operating Voltage: 1.5 V

Max Voltage (typical range): 1.575 V

Description

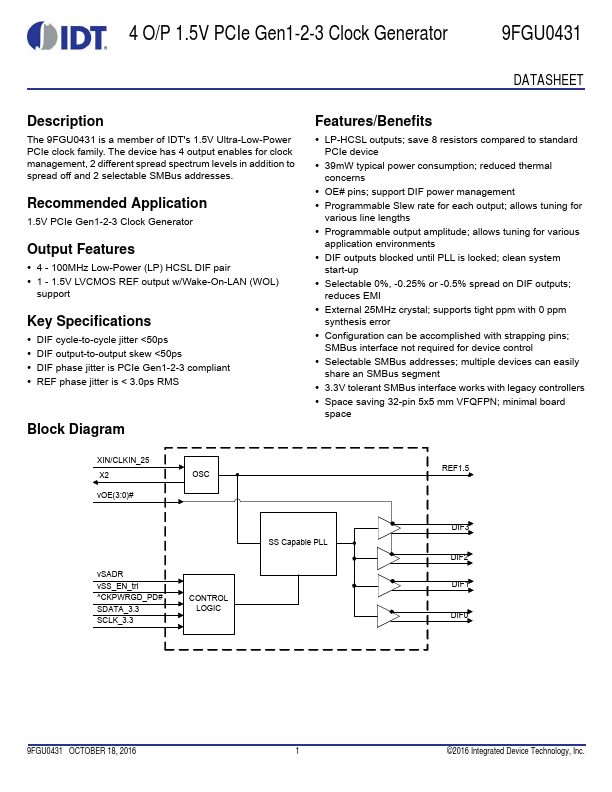

The 9FGU0431 is a member of IDT's 1.5V Ultra-Low-Power PCIe clock family. The device has 4 output enables for clock management, 2 different spread spectrum levels in addition to spread off and 2 selectable SMBus addresses.

Key Features

- 4 - 100MHz Low-Power (LP) HCSL DIF pair

- 1 - 1.5V LVCMOS REF output w/Wake-On-LAN (WOL) support Key Specifications

- DIF cycle-to-cycle jitter <50ps

- DIF output-to-output skew <50ps

- DIF phase jitter is PCIe Gen1-2-3 compliant

- REF phase jitter is < 3.0ps RMS