CPS-1848

CPS-1848 is Gen2 RapidIO Switch manufactured by IDT.

Description

The CPS-1848 (80HCPS1848) is a Rapid IO Specification (Rev. 2.1) pliant Secure Packet Switch whose functionality is central to routing packets for distribution among DSPs, processors, FPGAs, other switches, or any other Rapid IO-based devices. It can also be used in Rapid IO backplane switching. The CPS-1848 supports Serial Rapid IO (S-RIO) packet switching (unicast, multicast, and an optional broadcast) from any of its 18 input ports to any of its 18 output ports.

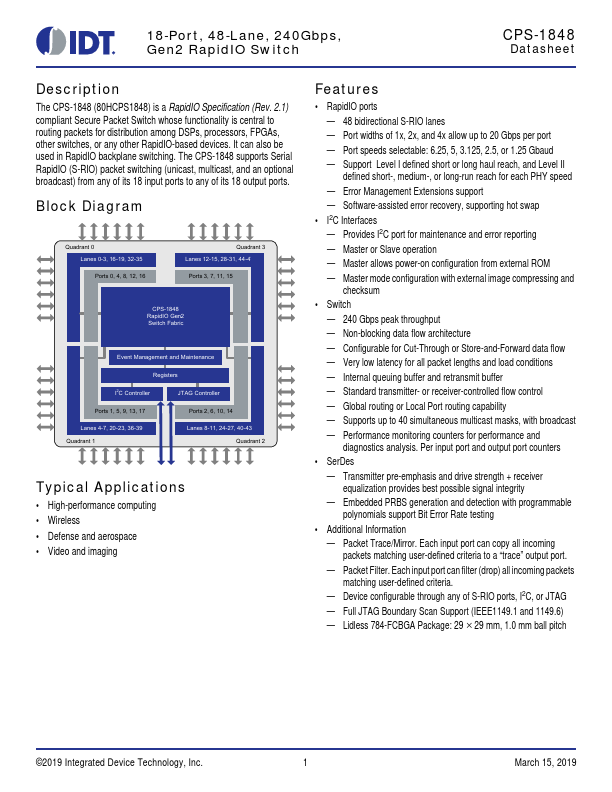

Block Diagram

Quadrant 0 Lanes 0-3, 16-19, 32-35

Ports 0, 4, 8, 12, 16

Quadrant 3 Lanes 12-15, 28-31, 44-47

Ports 3, 7, 11, 15

CPS-1848 Rapid IO Gen2 Switch Fabric

Event Management and Maintenance

Registers

I2C Controller

JTAG Controller

Ports 1, 5, 9, 13, 17 Lanes 4-7, 20-23, 36-39 Quadrant 1

Ports 2, 6, 10, 14 Lanes 8-11, 24-27, 40-43

Quadrant 2

Typical Applications

- High-performance puting

- Wireless

- Defense and aerospace

- Video and imaging

Features

- Rapid IO ports

- 48 bidirectional S-RIO lanes

- Port widths of 1x, 2x, and 4x allow up to 20 Gbps per port

- Port speeds selectable: 6.25, 5, 3.125, 2.5, or 1.25 Gbaud

- Support Level I defined short or long haul reach, and Level II defined short-, medium-, or long-run reach for each PHY speed

- Error Management Extensions support

- Software-assisted error recovery, supporting hot swap

- I2C Interfaces

- Provides I2C port for maintenance and error reporting

- Master or Slave operation

- Master allows power-on configuration from external ROM

- Master mode configuration with external image pressing and checksum

- Switch

- 240 Gbps peak throughput

- Non-blocking data flow architecture

- Configurable for Cut-Through or Store-and-Forward data flow

- Very low latency for all packet lengths and load conditions

- Internal queuing buffer and retransmit buffer

- Standard transmitter- or receiver-controlled flow...