ICS9UMS9610 Datasheet Text

PC MAIN CLOCK

Remended Application:

Poulsbo Based Ultra-Mobile PC (UMPC)

- CK610

Output Features

:

- 3

- CPU low power differential push-pull pairss

- 3

- SRC low power differential push-pull pairs

- 1

- LCD100 SSCD low power differential push-pull pair

- 1

- DOT96 low power differential push-pull pair

- 1

- REF, 14.31818MHz, 3.3V SE output

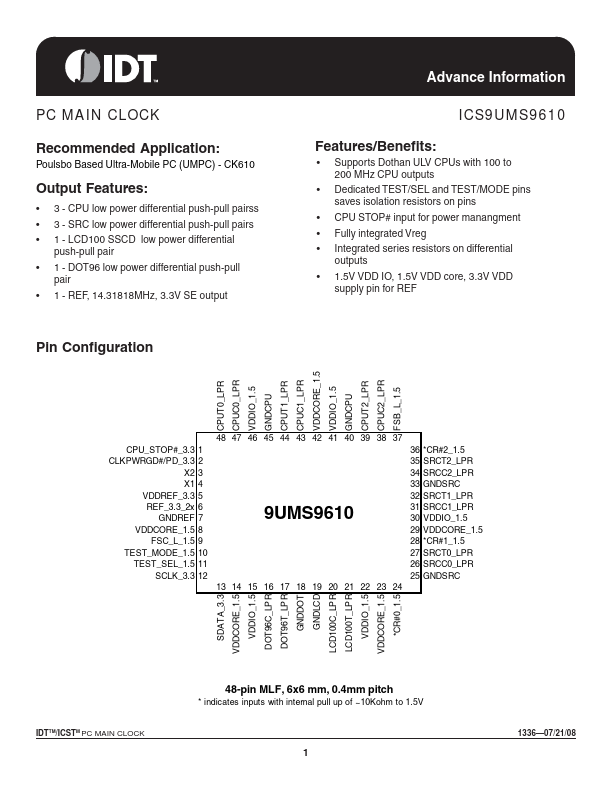

Pin Configuration

Advance Information

ICS9UMS9610

Features

/Benefits:

- Supports Dothan ULV CPUs with 100 to 200 MHz CPU outputs

- Dedicated TEST/SEL and TEST/MODE pins saves isolation resistors on pins

- CPU STOP# input for power manangment

- Fully integrated Vreg

- Integrated series resistors on differential outputs

- 1.5V VDD IO, 1.5V VDD core, 3.3V VDD supply pin for REF

CPUT0_LPR CPUC0_LPR VDDIO_1.5 GNDCPU CPUT1_LPR CPUC1_LPR VDDCORE_1.5 VDDIO_1.5 GNDCPU CPUT2_LPR CPUC2_LPR FSB_L_1.5

48 47 46 45 44 43 42 41 40 39 38 37

CPU_STOP#_3.3 1...