IDT54AHCT645

IDT54AHCT645 is High Speed CMOS Non-Inverting Buffer Transceiver manufactured by IDT.

- Part of the IDT74AHCT645 comparator family.

- Part of the IDT74AHCT645 comparator family.

FEATURES

:

- Equivalent to ALS speeds and output drive over full temperature and voltage supply extremes

- 8ns typical data to output delay

- IOL = 14m A over full military temperature range

- CMOS power levels (5p.W typo static)

- 80th CMOS and TTL output patible

- Substantially lower input current levels than ALS (5p.A max.)

- Non-inverting buffer transceiver

- 100% product assurance screening to MIL-STD-883, Class 8 is available

- JEDEC standard pinout for DIP and LCC

DESCRIPTION

:

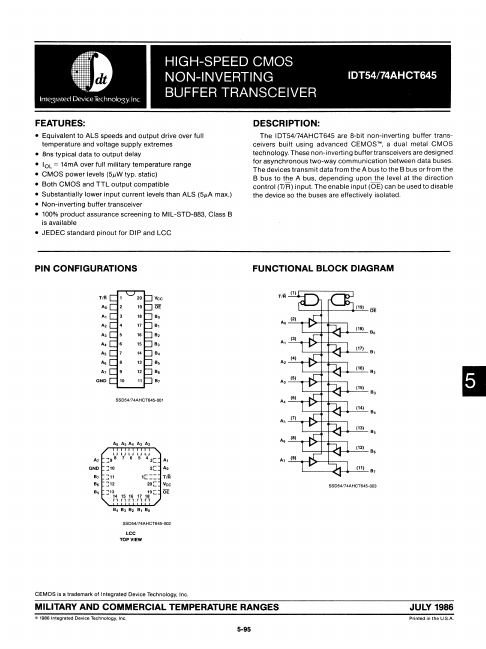

The IDT54174AHCT645 are 8-bit non-inverting buffer transceivers built using advanced CEMOS'- , a dual metal CMOS technology. These non-inverting buffer transceivers are designed for asynchronous two-way munication between data buses. The devices transmit data from the A bus to the 8 bus or from the 8 bus to the A bus, depending upon the level at the direction control (Ti Fi) input. The enable input (OE) can be used to disable the device so the buses are effectively isolated.

PIN...