IDT70V9359L Overview

Key Features

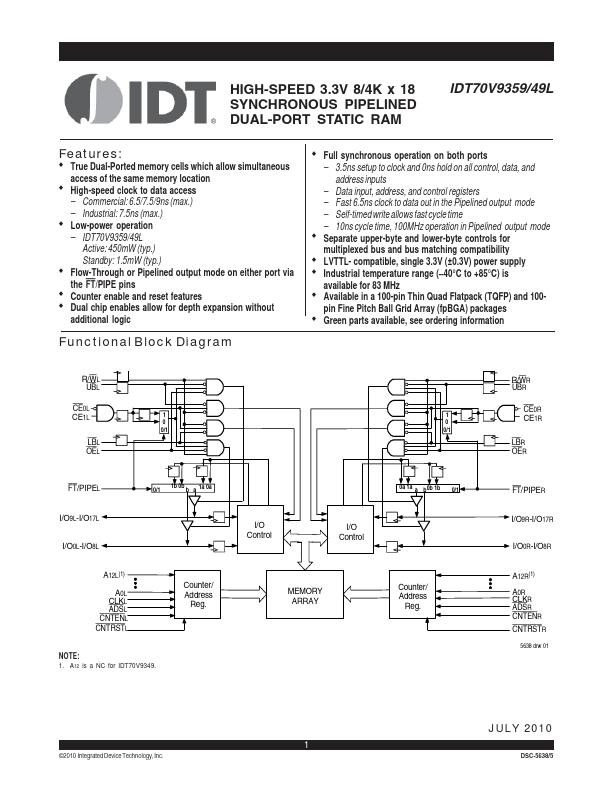

- True Dual-Ported memory cells which allow simultaneous access of the same memory location

- High-speed clock to data access – Commercial: 6.5/7.5/9ns (max.) – Industrial: 7.5ns (max.)

- Low-power operation – IDT70V9359/49L Active: 450mW (typ.) Standby: 1.5mW (typ.)

- Flow-Through or Pipelined output mode on either port via the FT/PIPE pins

- Counter enable and reset features

- Dual chip enables allow for depth expansion without additional logic