IDT72261LA

IDT72261LA is CMOS FIFO memories manufactured by IDT.

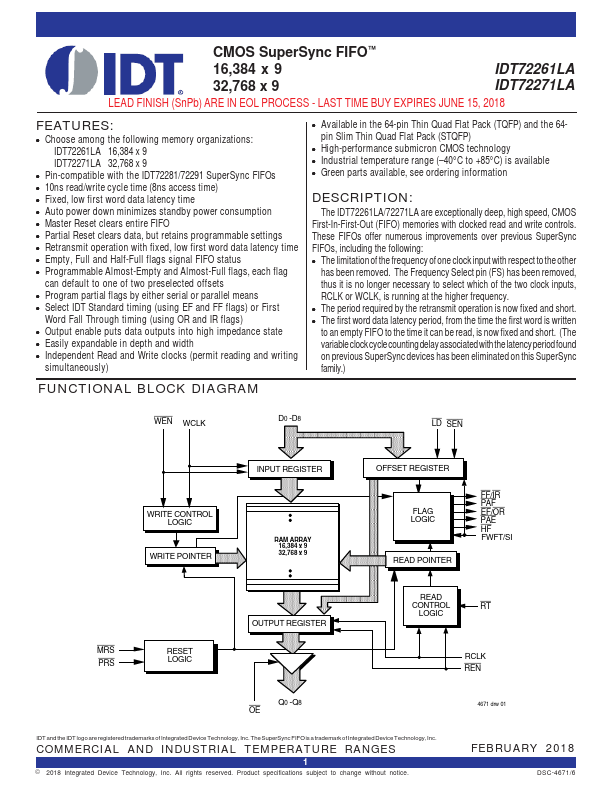

CMOS Super Sync FIFO™

16,384 x 9

32,768 x 9

IDT72271LA

LEAD FINISH (Sn Pb) ARE IN EOL PROCESS

- LAST TIME BUY EXPIRES JUNE 15, 2018

Features

:

- Choose among the following memory organizations: IDT72261LA 16,384 x 9 IDT72271LA 32,768 x 9

- Pin-patible with the IDT72281/72291 Super Sync FIFOs

- 10ns read/write cycle time (8ns access time)

- Fixed, low first word data latency time

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Retransmit operation with fixed, low first word data latency time

- Empty, Full and Half-Full flags signal FIFO status

- Programmable Almost-Empty and Almost-Full flags, each flag can default to one of two preselected offsets

- Program partial flags by either serial or parallel means

- Select IDT Standard timing (using EF and FF flags) or First

Word Fall Through timing (using OR and IR flags)

- Output enable puts...