IDT8P34S1102I

Overview

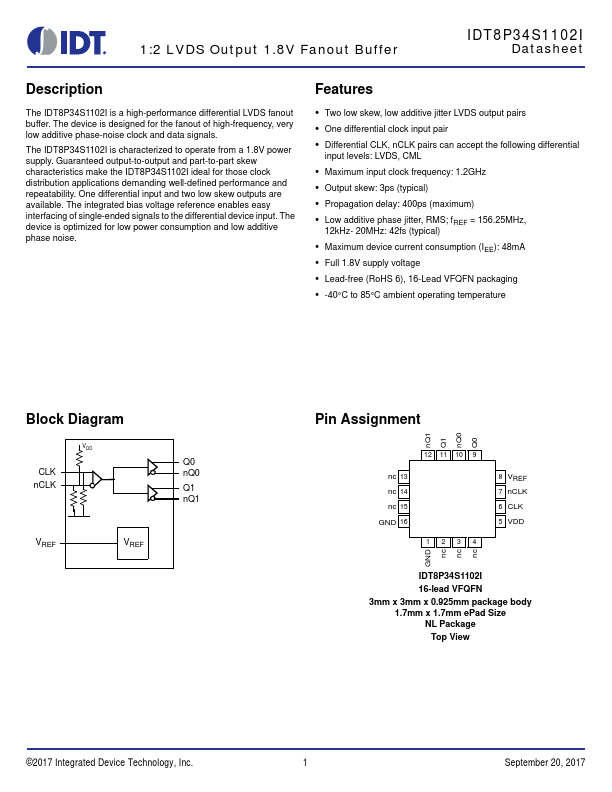

The IDT8P34S1102I is a high-performance differential LVDS fanout buffer. The device is designed for the fanout of high-frequency, very low additive phase-noise clock and data signals.

- Two low skew, low additive jitter LVDS output pairs

- One differential clock input pair

- Differential CLK, nCLK pairs can accept the following differential input levels: LVDS, CML

- Maximum input