MX0141VA0

MX0141VA0 is 1:4 High-Speed / Low-Speed Multiplexer Pair manufactured by IDT.

Description

Important: All parameters in this short-form datasheet are prior to device characterization and are currently subject to change. Final parameters will be updated after device characterization.

The MX0141VA0 is prised of a high-speed, 1:4 multiplexer (mux) path and a low-speed, 1:4 mux path.

The high-speed path is a bidirectional 12-bit port 1:4 mux. The lowspeed path is a unidirectional 4-bit port 1:4 mux. Both high-speed and low-speed paths support SSTL_12 and SSTL_18 signaling.

Both paths are controlled in an identical manner using the input control signals: SEL1, SEL0, and EN_B. For example, when EN_B is asserted LOW, one of the high-speed [ABCD] ports is connected to IN while all the remaining ports are tri-stated. When input EN_B is HIGH all four [ABCD] ports are tri-stated.

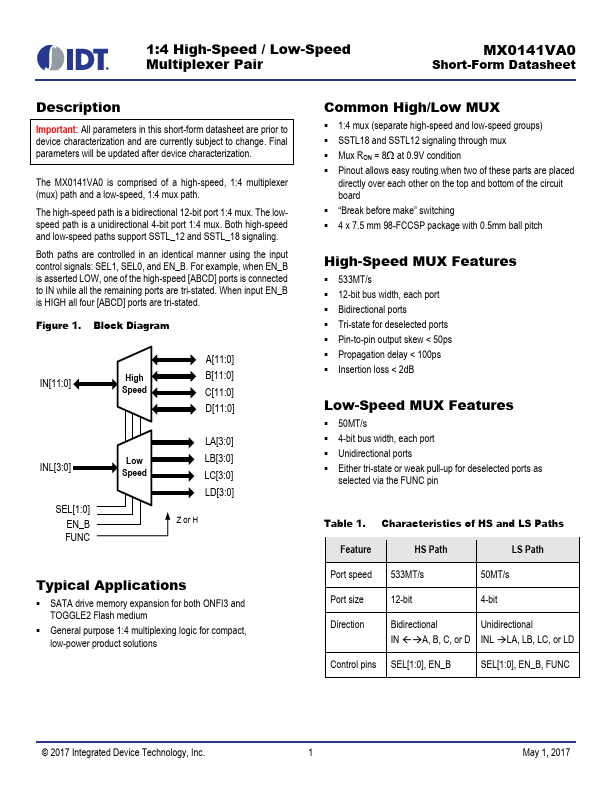

Figure 1. Block Diagram

IN[11:0]

High Speed

A[11:0] B[11:0] C[11:0] D[11:0]

INL[3:0]

SEL[1:0] EN_B FUNC

Low Speed

LA[3:0] LB[3:0] LC[3:0] LD[3:0]

Z or H

Typical Applications

- SATA drive memory expansion for both ONFI3 and TOGGLE2 Flash medium

- General purpose 1:4 multiplexing logic for pact, low-power product solutions mon High/Low MUX

- 1:4 mux (separate high-speed and low-speed groups)

- SSTL18 and SSTL12 signaling through mux

- Mux RON = 8 at 0.9V condition

- Pinout allows easy routing when two of these parts are placed directly over each other on the top and bottom of the circuit board

- “Break before make” switching

- 4 x 7.5 mm 98-FCCSP package with 0.5mm ball pitch

High-Speed MUX Features

- 533MT/s

- 12-bit bus width, each port

- Bidirectional ports

- Tri-state for deselected ports

- Pin-to-pin output skew < 50ps

- Propagation delay < 100ps

- Insertion loss < 2d B

Low-Speed MUX Features

- 50MT/s

- 4-bit bus width, each port

- Unidirectional ports

- Either tri-state or weak pull-up for deselected ports as selected via the FUNC pin

Table 1. Characteristics of HS and LS Paths

Feature

HS Path

LS...