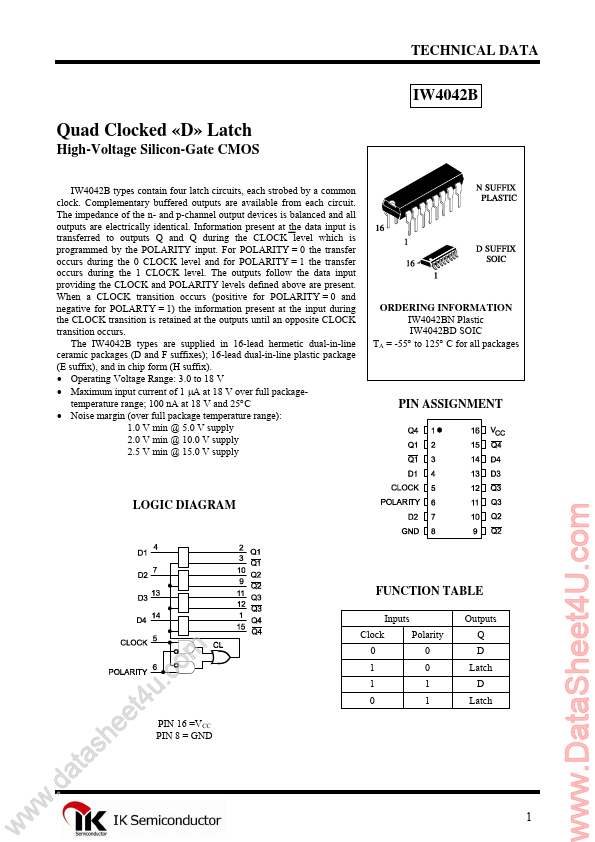

IW4042B

TECHNICAL DATA

Quad Clocked «D» Latch

High-Voltage Silicon-Gate CMOS

IW4042B types contain four latch circuits, each strobed by a mon clock. plementary buffered outputs are available from each circuit. The impedance of the n- and p-channel output devices is balanced and all outputs are electrically identical. Information present at the data input is transferred to outputs Q and Q during the CLOCK level which is programmed by the POLARITY input. For POLARITY = 0 the transfer occurs during the 0 CLOCK level and for POLARITY = 1 the transfer occurs during the 1 CLOCK level. The outputs follow the data input providing the CLOCK and POLARITY levels defined above are present. When a CLOCK transition occurs (positive for POLARITY = 0 and negative for POLARTY = 1) the information present at the input during the CLOCK transition is retained at the outputs until an opposite CLOCK transition occurs. The IW4042B types are supplied in 16-lead hermetic dual-in-line ceramic packages (D and...