IS43LD32800B

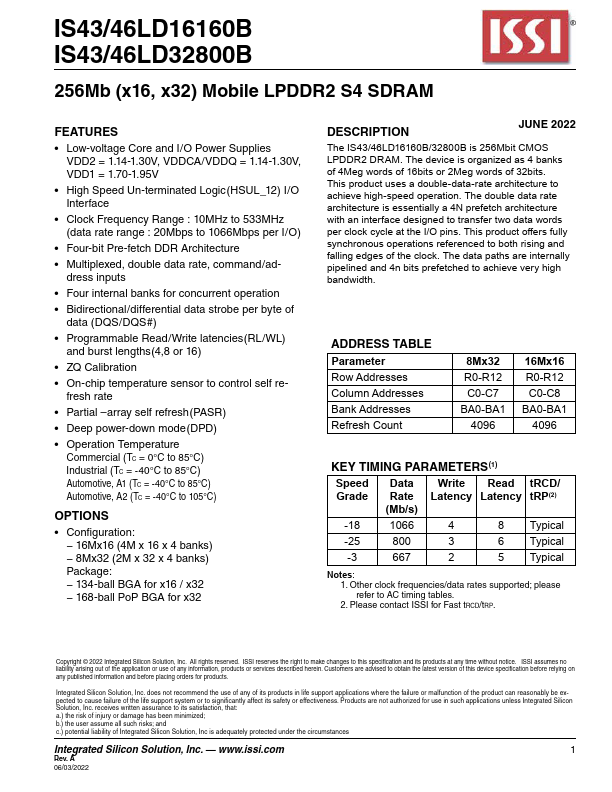

FEATURES

- Low-voltage Core and I/O Power Supplies VDD2 = 1.14-1.30V, VDDCA/VDDQ = 1.14-1.30V, VDD1 = 1.70-1.95V

- High Speed Un-terminated Logic(HSUL_12) I/O Interface

- Clock Frequency Range : 10MHz to 533MHz (data rate range : 20Mbps to 1066Mbps per I/O)

- Four-bit Pre-fetch DDR Architecture

- Multiplexed, double data rate, mand/address inputs

- Four internal banks for concurrent operation

- Bidirectional/differential data strobe per byte of data (DQS/DQS#)

- Programmable Read/Write latencies(RL/WL) and burst lengths(4,8 or 16)

- ZQ Calibration

- On-chip temperature sensor to control self refresh rate

- Partial

- array self refresh(PASR)

- Deep power-down mode(DPD)

- Operation Temperature mercial (TC = 0°C to 85°C) Industrial (TC = -40°C to 85°C) Automotive, A1 (TC = -40°C to 85°C) Automotive, A2 (TC = -40°C to 105°C)

OPTIONS

- Configuration:

- 16Mx16 (4M x 16 x 4 banks)

- 8Mx32 (2M x 32 x 4 banks) Package:

- 134-ball BGA for x16 / x32

- 168-ball Po P BGA for x32

DESCRIPTION

JUNE...