IS67WVH8M8BLL

IS67WVH8M8BLL is 8M x 8 HyperRAM manufactured by ISSI.

- Part of the IS66WVH8M8ALL comparator family.

- Part of the IS66WVH8M8ALL comparator family.

Overview

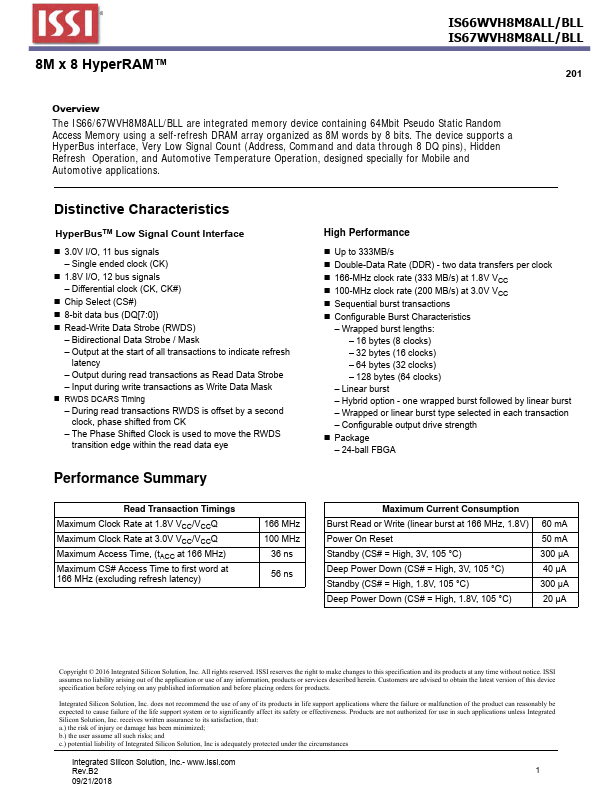

The IS66/67WVH8M8ALL/BLL are integrated memory device containing 64Mbit Pseudo Static Random Access Memory using a self-refresh DRAM array organized as 8M words by 8 bits. The device supports a Hyper Bus interface, Very Low Signal Count (Address, mand and data through 8 DQ pins), Hidden Refresh Operation, and Automotive Temperature Operation, designed specially for Mobile and Automotive applications.

Distinctive Characteristics

Hyper Bus TM Low Signal Count Interface

- 3.0V I/O, 11 bus signals

- Single ended clock (CK)

- 1.8V I/O, 12 bus signals

- Differential clock (CK, CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Read-Write Data Strobe (RWDS)

- Bidirectional Data Strobe / Mask

- Output at the start of all transactions to indicate refresh latency

- Output during read transactions as Read Data Strobe

- Input during write transactions as Write Data Mask

- RWDS DCARS Timing

- During read transactions RWDS is offset by a second clock, phase shifted from CK

- The Phase Shifted Clock is used to move the RWDS transition edge within the read data eye

Performance Summary

High Performance

- Up to 333MB/s

- Double-Data Rate (DDR)

- two data transfers per clock

- 166-MHz clock rate (333 MB/s) at 1.8V VCC

- 100-MHz clock rate (200 MB/s) at 3.0V VCC

- Sequential burst transactions

- Configurable Burst Characteristics

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- 128 bytes (64 clocks)

- Linear burst

- Hybrid option

- one wrapped burst followed by linear burst

- Wrapped or linear burst type selected in each transaction

- Configurable output drive strength

- Package

- 24-ball FBGA

Read Transaction...