ICS2509C

ICS2509C is manufactured by Integrated Circuit Systems.

Integrated Circuit Systems, Inc.

3.3V Phase-Lock Loop Clock Driver

General Description

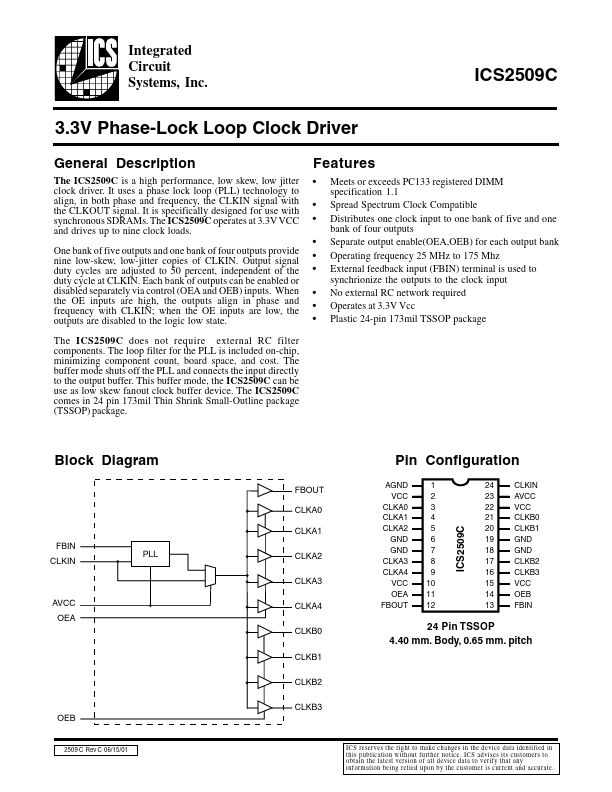

The ICS2509C is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs. The ICS2509C operates at 3.3V VCC and drives up to nine clock loads. One bank of five outputs and one bank of four outputs provide nine low-skew, low-jitter copies of CLKIN. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLKIN. Each bank of outputs can be enabled or disabled separately via control (OEA...