ICS527-04

Description

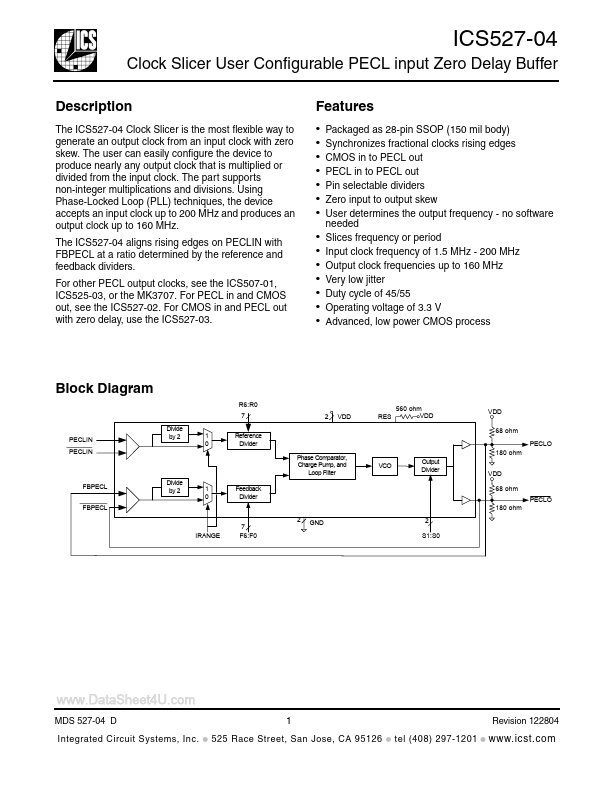

The ICS527-04 Clock Slicer is the most flexible way to generate an output clock from an input clock with zero skew. The user can easily configure the device to produce nearly any output clock that is multiplied or divided from the input clock. The part supports non-integer multiplications and divisions. Using Phase-Locked Loop (PLL) techniques, the device accepts an input clock up to 200 MHz and produces an output clock up to 160 MHz. The ICS527-04 aligns rising edges on PECLIN with FBPECL at a ratio determined by the reference and feedback dividers. For other PECL output clocks, see the ICS507-01, ICS525-03, or the MK3707. For PECL in and CMOS out, see the ICS527-02. For CMOS in and PECL out with zero delay, use the ICS527-03.

Features

- -

- -

- -

- -

- -

- -

- -

Packaged as 28-pin SSOP (150 mil body) Synchronizes fractional clocks rising edges CMOS in to PECL out PECL in to PECL out Pin selectable dividers Zero input to output skew User determines the output frequency

-...