ICS83054I-01 Overview

Description

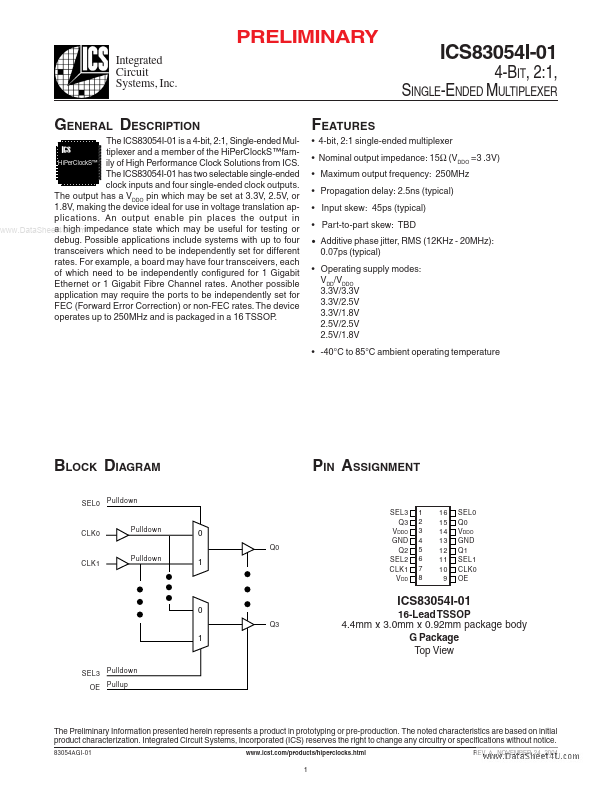

The ICS83054I-01 is a 4-bit, 2:1, Single-ended Multiplexer and a member of the HiPerClockS™famHiPerClockS™ ily of High Performance Clock Solutions from ICS. The ICS83054I-01 has two selectable single-ended clock inputs and four single-ended clock outputs.

Key Features

- 4-bit, 2:1 single-ended multiplexer

- Nominal output impedance: 15Ω (VDDO =3 .3V)

- Maximum output frequency: 250MHz

- Propagation delay: 2.5ns (typical)

- Input skew: 45ps (typical)

- Part-to-part skew: TBD

- Additive phase jitter, RMS (12KHz

- 20MHz): 0.07ps (typical)

- 40°C to 85°C ambient operating temperature ICS