ICS8344

ICS8344 is 1-TO-24 DIFFERENTIAL-TO-LVCMOS FANOUT BUFFER manufactured by Integrated Circuit Systems.

PRELIMINARY

Integrated Circuit Systems, Inc.

LOW SKEW, 1-TO-24 DIFFERENTIAL-TO-LVCMOS FANOUT BUFFER

Features

- 24 LVCMOS outputs, 7Ω typical output impedance

- Output frequency up to 167MHz

- 275ps output skew, 600ps part to part skew

- Translates any differential input signal (PECL, HSTL, LVDS) to LVCMOS without external bias networks

- Translates any single-ended input signal to LVCMOS with resistor bias on n CLK input

- Translates and inverts any single-ended input signal to LVCMOS with resistor bias on CLK input

- Multiple differential clock input pairs for redundant clock applications

- LVCMOS control inputs

- Multiple output enable pins for disabling unused outputs in reduced fanout applications

- 3.3V, 2.5V or mixed 3.3V, 2.5V operating supply modes

- 48 lead low-profile QFP(LQFP), 7mm x 7mm x 1.4mm package body, 0.5mm package lead pitch

- 0°C to 70°C ambient operating temperature

- Industrial temperature versions available upon request

GENERAL DESCRIPTION

The ICS8344 is a low voltage, low skew fanout buffer and a member of the Hi Per Clock S™ Hi Per Clock S™ family of High Performance Clock Solutions from ICS. The ICS8344 is designed to translate any differential signal levels to LVCMOS levels. The low impedance LVCMOS outputs are designed to drive 50Ω series or parallel terminated transmission lines. The effective fanout can be increased to 48 by utilizing the ability of the outputs to drive two series terminated lines. Redundant clock .. applications can make use of the dual clock input. The dual clock inputs also facilitate board level testing. ICS8344 is characterized at full 3.3V, full 2.5V and mixed 3.3V input and 2.5V output operating supply modes.

,&6

Guaranteed output and part-to-part skew characteristics make the ICS8344 ideal for those clock distribution applications demanding well defined performance and repeatability.

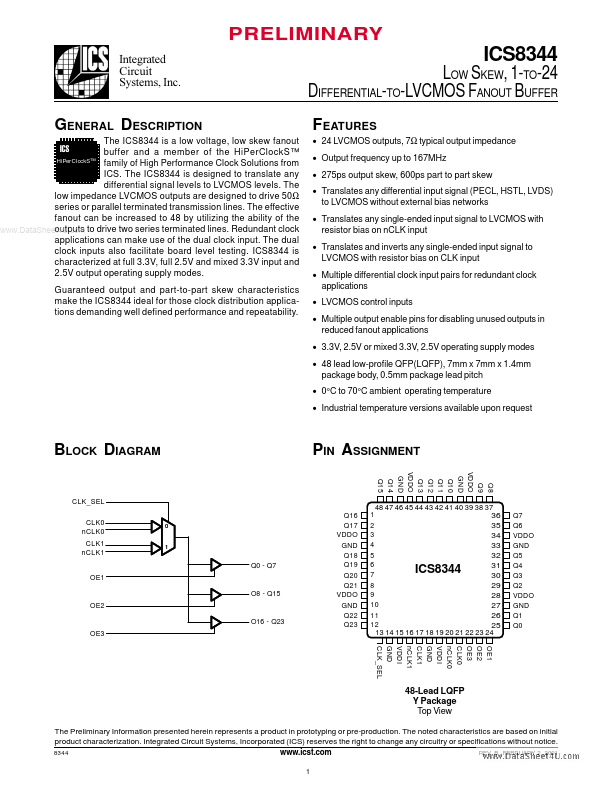

BLOCK DIAGRAM

PIN ASSIGNMENT

Q8 Q9 VDDO GND Q10 Q11 Q12 Q13 VDDO GND Q14 Q15

CLK_SEL CLK0 n CLK0 CLK1 n...