ICS9148-26

ICS9148-26 is Frequency Generator & Integrated Buffers manufactured by Integrated Circuit Systems.

Integrated Circuit Systems, Inc.

Frequency Generator & Integrated Buffers for PENTIUM/Pro TM

General Description

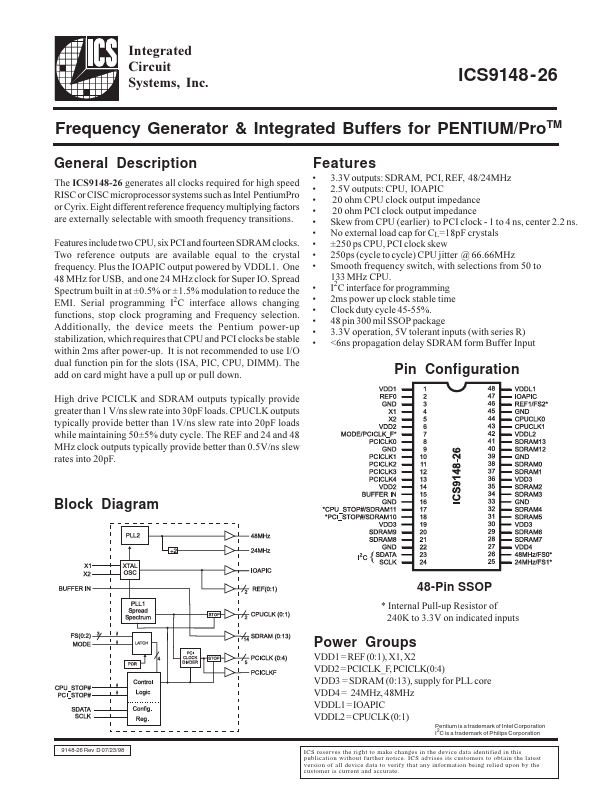

The ICS9148-26 generates all clocks required for high speed RISC or CISC microprocessor systems such as Intel Pentium Pro or Cyrix. Eight different reference frequency multiplying factors are externally selectable with smooth frequency transitions. Features include two CPU, six PCI and fourteen SDRAM clocks. Two reference outputs are available equal to the crystal frequency. Plus the IOAPIC output powered by VDDL1. One 48 MHz for USB, and one 24 MHz clock for Super IO. Spread Spectrum built in at ±0.5% or ±1.5% modulation to reduce the EMI. Serial programming I2C interface allows changing functions, stop clock programing and Frequency selection. Additionally, the device meets the Pentium power-up stabilization, which requires that CPU and PCI clocks be stable within 2ms after power-up. It is not remended to use I/O dual function pin for the slots (ISA, PIC, CPU, DIMM). The add on card might have a pull up or pull down. High drive PCICLK and SDRAM outputs typically provide greater than 1 V/ns slew rate into 30p F loads. CPUCLK outputs typically provide better than 1V/ns slew rate into 20p F loads while maintaining 50±5% duty cycle. The REF and 24 and 48 MHz clock outputs typically provide better than 0.5V/ns slew rates into 20p F.

Features

3.3V outputs: SDRAM, PCI, REF, 48/24MHz 2.5V outputs: CPU, IOAPIC 20 ohm CPU clock output impedance 20 ohm PCI clock output impedance Skew from CPU (earlier) to PCI clock

- 1 to 4 ns, center 2.2 ns. No external load cap for CL=18p F crystals ±250 ps CPU, PCI clock skew 250ps (cycle to cycle) CPU jitter @ 66.66MHz Smooth frequency switch, with selections from 50 to 133 MHz CPU. I2C interface for programming 2ms power up clock stable time Clock duty cycle 45-55%. 48 pin 300 mil SSOP package 3.3V operation, 5V tolerant inputs (with series R) <6ns propagation delay SDRAM form Buffer...