ICS9248-72

ICS9248-72 is Frequency Generator & Integrated Buffers manufactured by Integrated Circuit Systems.

Integrated Circuit Systems, Inc.

Preliminary Product Preview

Frequency Timing Generator for PENTIUM II Systems

General Description

The ICS9248-72 is a main clock synthesizer chip for Pentium II based systems using Rambus Interface DRAMs. This chip provides all the clocks required for such a system when used with a Direct Rambus Clock Generator(DRCG) chip such as the ICS9211-01. Spread Spectrum may be enabled by driving the SPREAD# pin active. Spread spectrum typically reduces system EMI by 8d B to 10d B. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS924872 employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature variations. The CPU/2 clocks are inputs to the DRCG.

Features

Up to 200MHz frequency support. Power Down feature. Spread Spectrum for EMI control (0 to 0.5% down spread , + 0.25% center spread) I2C interface. VDDL=2.5V,VDD=3.3V CPU Output Jitter: <250ps CPU/2 Output Jitter. <250ps IOAPIC Output Jitter: <500ps 48MHz, 3V66, PCI Output Jitter: <500ps Ref Output Jitter. <1000ps CPU Output Skew: <175ps IOAPIC Output Skew <250ps PCI Output Skew: <500ps 3V66 Output Skew <250ps CPU to 3V66 Output Offset: 0.0

- 1.5ns (CPU leads) 3V66 to PCI Output Offset: 1.5

- 4.0ns (3V66 leads) CPU to IOAPIC Output Offset 1.5

- 4.0ns (CPU leads)

Key Specification

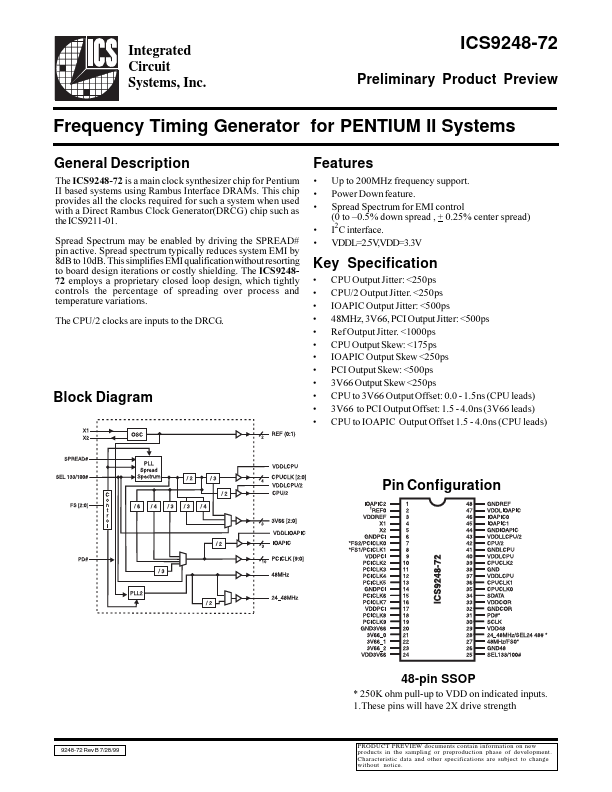

Block Diagram

Pin Configuration

48-pin SSOP

- 250K ohm pull-up to VDD on indicated inputs. 1.These pins will have 2X drive strength

9248-72 Rev B 7/28/99

PRODUCT PREVIEW documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Preliminary Product Preview

Power Groups:

VDDREF, GNDREF = REF, X1, X2 GNDPCI, VDDPCI = PCICLK VDD66, GND66 = 3V66 VDD48, GND48 = 48MHz VDDCOR, GNDCOR = PLL Core VDDLCPU/2 , GNDLCPU/2...