Datasheet Summary

Integrated Circuit Systems, Inc.

2.5V DDR/Zero Delay Fan Out Buffer (100MHz

- 225MHz)

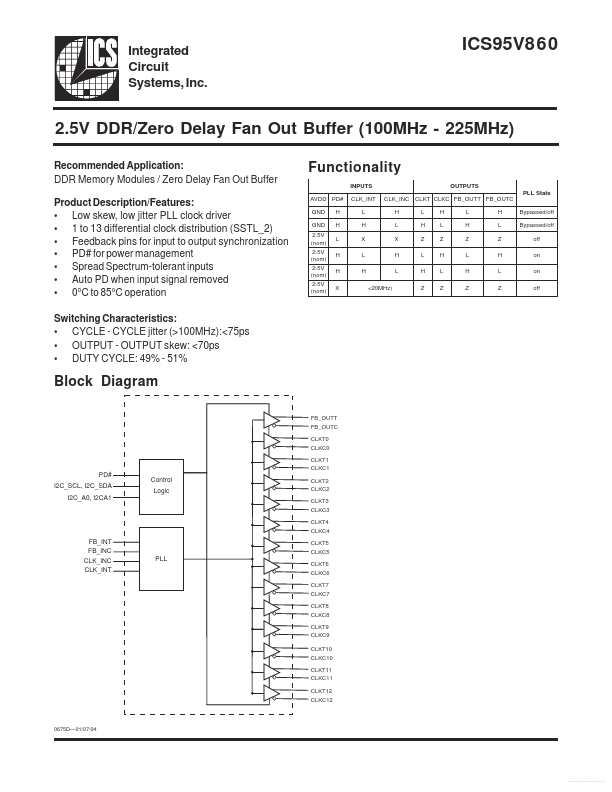

Remended Application: DDR Memory Modules / Zero Delay Fan Out Buffer Product Description/Features

:

- Low skew, low jitter PLL clock driver

- 1 to 13 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- PD# for power management

- Spread Spectrum-tolerant inputs

- Auto PD when input signal removed

- 0°C to 85°C operation Switching Characteristics:

- CYCLE

- CYCLE jitter (>100MHz):<75ps

- OUTPUT

- OUTPUT skew: <70ps

- DUTY CYCLE: 49%

- 51%

Functionality

INPUTS AVDD PD# GND GND 2.5V (nom) 2.5V (nom) 2.5V (nom) 2.5V (nom) H H L H H X CLK_INT L H X L H...